你好。 此客户正在使用 ADS127L21器件。

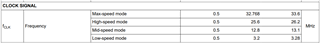

通过查看数据表、总共有4个 Speed_mode。

①max μ A 速度模式(Fclk=32.768Mhz)

①high Ω 速度模式(Fclk=25.6Mhz)

①mid μ s 速度模式(Fclk=12.8Mhz)

①low μ s 速度模式(Fclk=3.2Mhz)

在我们的情况下、必须考虑抗混叠、并且必须针对25.6K SPS 优化设计。

因此、我们将使用一个外部晶体振荡器13.1072Mhz。

对于 ADS127L21器件、可以使用单独的时钟、而不是仅限于数据表中所示时钟的四种类型吗?

或者我是否必须仅使用这4种类型的时钟?

由于情况紧急、请快速回复。

谢谢!