主题中讨论的其他器件: LMK04828

您好!

我们有一个带有 DAC39J82EVM 和 ZCU102的测试平台、 可以从 FPGA 端看到 JESD 总线上有一些活动、但我们看不到来自 DAC 的任何东西、同步信号从不发生变化。

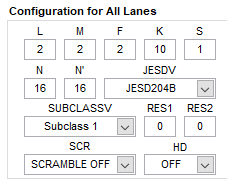

FPGA 上的 Xilinx JESD IP 配置为双通道链路、线路速度为6.144Gbps、使用 CPLL 具有307.2 MHz 的参考时钟。

我们要 在 JESD PHY 数据表中的 FPGA 上使用此时钟方案:

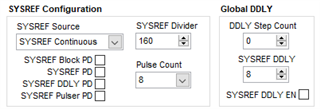

TI 电路板上的 LMK04828会生成 307.2 MHz CPLL 参考时钟和153.6 MHz 内核时钟(1/40线路速率)、这两个时钟都通过 FMC 连接器传递到 FPGA。 现在、我们让 SYSREF 是连续的。

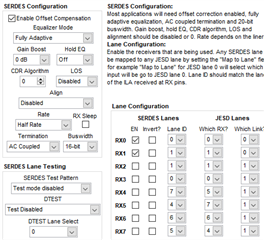

我们将使用 GUI 通过以下设置对 TI 板进行编程:

我们似乎没有收到任何警报:

然而、我们在 DAC 上没有看到任何输出。

我们正在使用此 JESD 配置、但我们不确定如何在 Xilinx JESD IP 上复制该配置:

非常感谢您提供任何帮助。 如有必要、我们可以提供更多详细信息。

胡安