请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS7953 主题中讨论的其他器件: ADS8686S

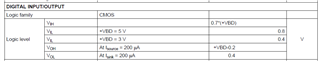

VDB = 1.8V 时的逻辑电平是多少? 具体来说是 VIL?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.