请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

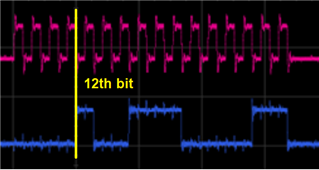

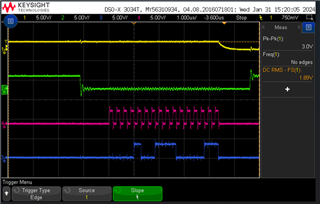

器件型号:DAC121S101 当我写入 DAC 时、输出电压出现压降。 我注意到一个问题、因此决定了测试。 将相同的值写入 DAC。 我不应该看到输出发生变化。 在某些写入期间、Vout 降至0。

黄色/顶部:DAC Vout = 2.0V

绿色/第二:芯片选择/同步

红色/3:时钟、3.4MHz

蓝色/底部:数据、2400 (9C3)

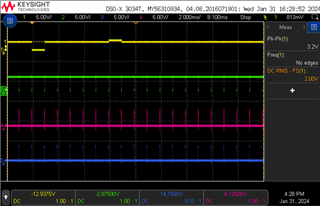

这不是稳定延迟、恰好在第16个时钟周期发生。 我测量了3.3V、而且没有看到压降。 似乎芯片复位了、但之后我捕获了它变为高电平、如图所示:

有什么建议吗? 谢谢