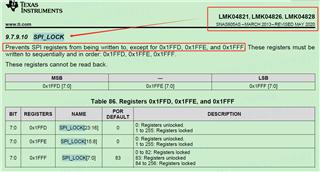

Other Parts Discussed in Thread: AFE58JD48, AFE58JD48EVM, LMK04826

主题中讨论的其他器件:AFE58JD48、、 LMK04826

我们目前正在评估采用 AFE58JD48EVM 的 AFE58JD48芯片的 AD 采集性能 。 但是、我们没有与 TSWxxx 相关的 EVM。 我们使用 zcu106 (Xilinx EVM)的 FMC 接口连接到 AFE58JD48EVM、 AFE58JD48EVM 的跳线配置如下:

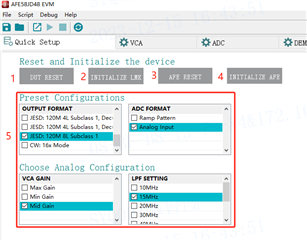

按照以下步骤对其进行设置

测量结果如下:

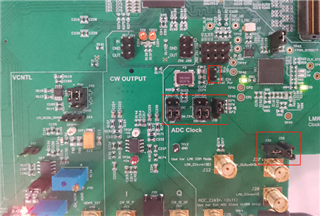

- LMK_ADC_CLKP--TP44: 平均电压约为1.25V,频率约为322MHz,Vpp 约为200mV。

- FPGA_CLK_OUT_P 没有时钟

- CLK_GTXP:平均电压约为1.25V,频率约为119MHz

- FPGA_SYSREFP: 平均电压约为1.239V,频率约为2.5MHz;

我的问题是:

- 为什么上面测量的所有时钟的直流偏置电压约为1.25V? 这是正常的吗?

- 根据 AFE58JD48EVM_User's Guide 和跳线配置、AFE 时钟为125MHz 或40MHz、但测量的 TP44-LMK_ADC_CLKP 为322MHz。 这是怎么一回事?

- 为什么 FPGA_CLK_OUT_P 没有输出时钟? 该时钟是对应于 JESD204B 接口的 glblk 还是 rx_core_clk?

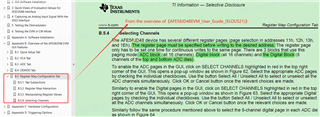

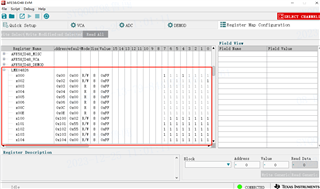

- 在以下配置中、120M 和 Dec 意味着什么? 如果要修改 JESD 参数、该怎么办? 例如、将其设置为 JESD 子类2、或更改 JESD 的时钟。

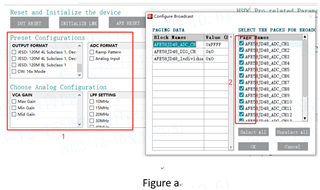

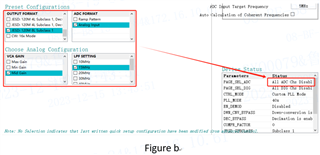

- 为什么图 A 中的配置1和配置2不同时存在? 在图 b 中、配置了 Preset Configurations 中的参数后、Device Status 会显示 All ADC CHS Disable。 在这种情况下、ADC 能够正常输出数据吗?

非常感谢您的回复!