Other Parts Discussed in Thread: ADC3643EVM

您好!

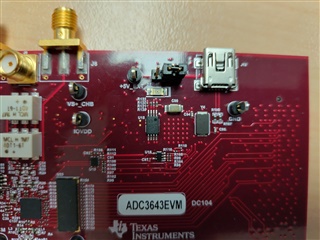

我当前正在尝试使用 Xilinx ZC702 FPGA 配置 ADC3643EVM。

为此、我需要使用 FMC 连接器的 SDIO_I、SDIO_O、SEN、SDIO_OE 和 SCLK 引脚。

在提供的原理图中、这些引脚通过电阻器 R90至 R94和 R96至 R100连接到 ADC、必须不焊接、这是正确的吗?

但是、我没有在电路板上看到电阻 R90至 R94、光绘文件与提供的原理图和最新版本的电路板(修订版 E)之间是否进行了任何修改?

如果是,是否有任何其他重要的修改需要强调?