主题中讨论的其他器件: LMK04832

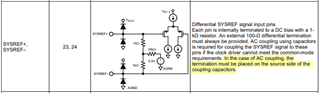

我们有一个模块设计、其 ADC16DX370在368.64 MHz 下运行、并连接到 Xilinx Ultrascale+ FPGA。 我们有多个 ADC 模块运行良好、但我们看到了来自多个电路板的奇怪但一致的故障。 故障电路板通过按预期将 SYNCb 线路拉低来初始化 JESD 同步、但在 FPGA 生成所需的 K28.5码字后绝不会退出初始化。 (syncb 线始终保持低电平)。 通过查看器件的寄存器转储(在任何初始化之前)、并比较"正在工作"与"未工作"模块、我们可以看到寄存器位0x6C[2](PLL_LOCK)在不工作的板上为低电平、在工作板上为高电平。 我没有看到任何有关器件中 PLL 的文档、因此我假设它是 JESD 接口的 PLL。 输入时钟是 LVDS、368.64 MHz、我们已经在示波器上验证了它的完整性。 该时钟由 LMK04832生成。 LMK 部件有一个可编程的 IO 标准。 如果我们使用互补 CMOS 标准对输入时钟进行过驱动、器件会很好地同步 JESD、但时钟的峰峰值电压超出器件的参数范围、因此我们想更好地了解这里发生了什么情况。 我们正在按照数据表第10.1节中定义的顺序初始化电源轨、并验证了它们是无噪声电源。 TI 能否提供更多信息、帮助我们了解 LVDS 为什么不起作用、以及 PLL_LOC=0意味着什么? 谢谢你。