我正在从事一个 PCB 设计、其中我有2个 ADS127L11菊花链。

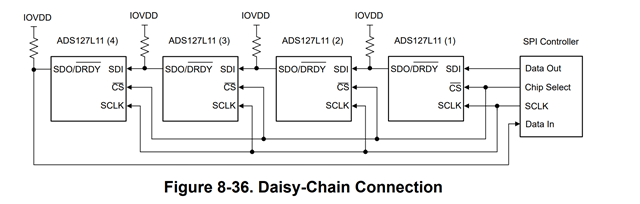

数据表的图8-36显示了一个示例:

该图显示了每个连接到 IOVDD 的 SDO->SDI 线路、并带有一个上拉电阻器。 但是、我在数据表的其他位置找不到任何建议值、也找不到有关该上拉电阻的任何其他说明。 评估板设计似乎也没有上拉电阻器。

数据表中唯一提到可能需要上拉电阻的地方是它提到当 CS 未激活时 SDO/DRDY 线为高阻态。 不过、我不太明白为什么 SDO 在该点的状态很重要、因为总线没有参与。 此外、与微处理器输入引脚类似的 SDI 引脚是否有弱上拉(100k?)的可能性 它无论如何会设置这条线的状态?

为了上下文、我将在 SDO/DRDY 引脚为单功能 SDO 的模式下使用 ADS。

感谢您提供的任何背景信息、以了解是否需要我们提供帮助。