大家好、

希望您做得好。

如何在不使用抽取的情况下实现两个不同 ADC3683之间的同步采样? 两个 ADC3683的输入信号已同时修整。

期待您的回复。

BRS、

达信

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Rob:

感谢您的帮助。 是的、客户尝试 同时提供两款不同器件的样片。 输入来自功率分频器、因此它们是完全相同的。 输出将会交错。

客户问如何保证两个 ADC3683同时采样?

无论如何,他们都需要创建一个将所有模拟输入连接在一起的模拟输入网络。

根据上述内容、分压器用于输入。

如果他们计划求和,则他们需要在时钟上执行同样的操作,如果他们计划进行交错,则您需要在每个时钟/设备之间设置移相器。

对于上述内容、您是说客户需要做的是应用 所需的 输入和时钟、ADC3683将会正常工作。 不需要任何其他配置? 就像其他一些用于同步的 SYNC 引脚一样?

BRS、

达信

达信、您好!

你们中有些人的评论不正确。

请阅读这篇较早的文章、了解 ADC 求和与交错 ADC 之间的区别。

所有时钟和模拟输入都需要来自一个源、并且必须具有匹配的长度、但进行交错时、需要对每个 ADC 之间的时钟进行相移、如下面的链接所述。

www.analogue.com/.../multichannel-a-d-converters.html

此致、

Rob

尊敬的 Rob:

谢谢你这么多的答复。 此应用手册与实际用法之间存在一些差异。

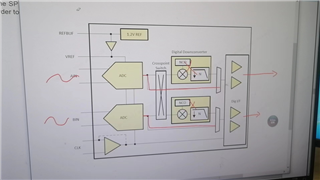

我们 没有 使用交叉 两个通道。 我们将 分别使用2个 ADC3683采样信号。 两个3683之间共有4个通道。 每个通道以相同的相位对相同的正弦波进行采样。 测试的结果是、两个3683输出的波形相位有时会不同步。 由于 我们还没有看到 ADC3683内的任何 NCO 和下采样模式、因此手册中提到的 SYNC 引脚不能用作同步芯片的同步引脚。 那么、在这种情况下、我们的问题是 ADC3683是否支持同步、如果支持、如何确保输出同步?

期待您的回复、谢谢!

BRS

达信

达信、我刚才与 Rob 谈过这件事、因此我将代表他发布消息。

我们仍然对系统设计不确定。 例如、在上面的消息中、您会提到输入来自功率分压器。 这是模拟输入通道还是时钟输入?

如果时钟输入对齐、则保证 ADC 在完全相同的实例中存储采样、只要时钟布线完全相同。 在上述条件下、数据不会在 FPGA 上对齐的唯一原因是与器件之间的 DCLKIN 阶段有关。 DCLKIN、DCLK 和 FCLK 如何路由? FPGA 在所有这些输入上都满足时序要求至关重要。

我们也不能完全理解信号偶尔会不同步的含义。 您是否可以指定更多信息、偶尔还可以共享好的和坏的捕获的图像?

谢谢,Chase