Other Parts Discussed in Thread: ADC3643EVM

您好!

我当前正在尝试使用 ADC3643EVM、但当我使用示波器检查 DCLK 输出引脚时、我会看到以下情况:

由于测量范围为-10ms 至~15ms、因此它是频率非常慢的信号。

我的卡是否有问题、或者它是否只是因为我没有正确配置(我没有配置任何内容、只是使用默认配置)。

下面是我的设置:

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADC3643EVM

您好!

我当前正在尝试使用 ADC3643EVM、但当我使用示波器检查 DCLK 输出引脚时、我会看到以下情况:

由于测量范围为-10ms 至~15ms、因此它是频率非常慢的信号。

我的卡是否有问题、或者它是否只是因为我没有正确配置(我没有配置任何内容、只是使用默认配置)。

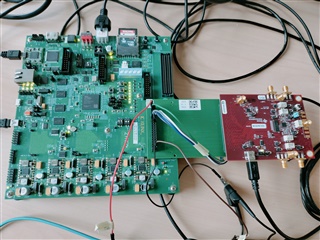

下面是我的设置:

谢谢。

尊敬的 Fabien:

您需要通过 GUI 配置器件、并提供硬件复位以及启用板载时钟。

您可以按照用户指南中概述的步骤开始使用: ADC364xEVM 用户指南

谢谢!

谢谢、

Fadi

尊敬的 Fabien:

FTDI 芯片已激活、这是 GUI 与不同 IC 进行通信的方式。 FTDI 连接到 USB、我们通过它连接 I2C 和 SPI 位。

您指出的电阻器仅适用于通过 FPGA (来自 FMC)的 I2C。

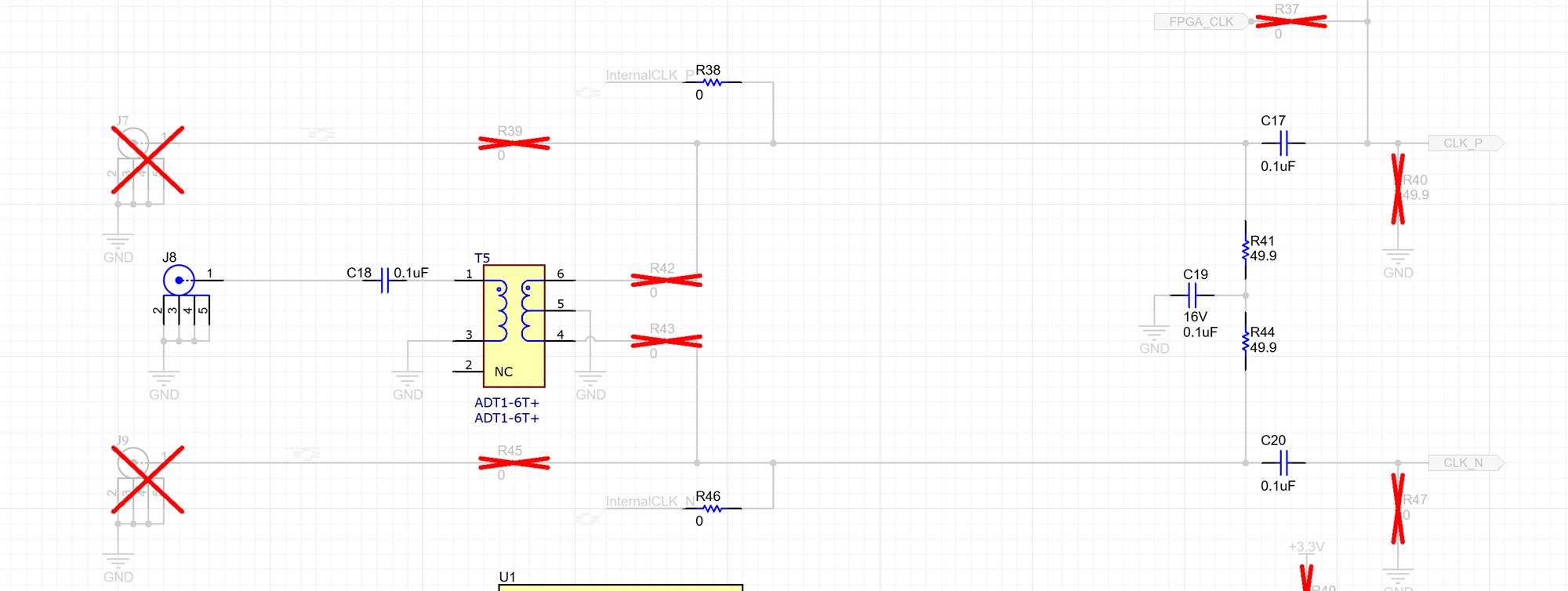

最简单的解决方案是将电路板修改为接受外部时钟。 如果您不计划使用串行模式、则只需提供外部采样时钟。 您需要修改以下片段以接受来自 SMA 连接器的单端或差分时钟。

谢谢!

谢谢、

Fadi