Other Parts Discussed in Thread: DAC8568, TL074H

主题中讨论的其他器件: TL074H

您好!

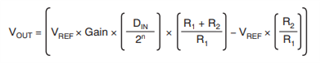

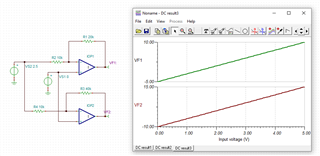

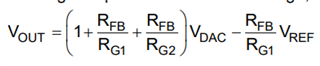

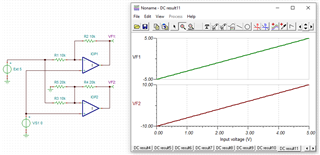

浏览了 DAC8568 数据表我仍然不完全清楚以下输入参数组合将如何影响任何双极运算设计:

- DAC8568C/D、即数据表中的增益=2等、但是...

- AVDD 目前至少设置为+3.3V、继而相应地限制 Vout。

- 使用内部2.5V 基准(另表示:在外部针对 ADC 重复使用)。

- 两个所需的输出范围取决于 DAC 输出引脚、+/-10V 或+/-5V、两者都通过 TL074H 运算放大器。

在数据表的第50-51页的9.2.1.1.3章中提供的示例主要集中在 AVdd +5V 时的 DAC8568A/B (GAIN=1等)和使用一个外部+5V 基准、但是对于上述情况(?)、看起来不够详细/明确。 有人有进一步的见解可以分享这个主题吗?

https://www.ti.com/lit/ds/symlink/dac8568.pdf

(+ https://www.ti.com/lit/an/slaa869/slaa869.pdf ?)

提前感谢、

BR//Karl