Other Parts Discussed in Thread: AFE5816

您好!

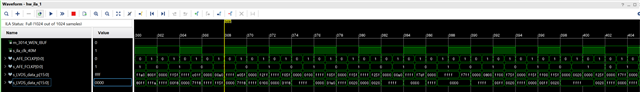

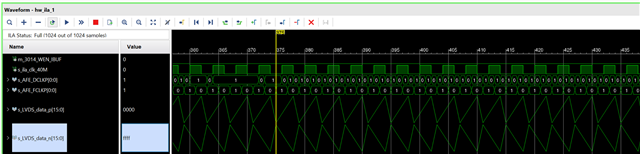

我曾尝试通过 AFE5816器件的测试模式验证 LVDS 时序、但在使用 Vivado 的 ILA 进行检查后、发现其不正确显示。 经过进一步检查、发现 DCLK 未正常运行。 AFE 的 ADC 时钟输入确认为40MHz 差分时钟、工作正常、FCLK 也确认为在40MHz 上正确输出。 下图是通过 ILA 检查斜坡测试模式的结果。 在考虑到12位串行化因子和12位量化的情况下、我预计频率是 FCLK 频率的6倍、但确认它没有正确显示。 还确认了它在电路板上也无法正常运行。 是否存在只有 DCLK 不工作的原因? 我很感谢您的答复。