Other Parts Discussed in Thread: DAC8801, DAC8811, DAC8812

主题中讨论的其他器件:DAC8801、 DAC8811、

团队、

客户报告不同数据表中的以下连线。

您能评论一下吗?

1) DAC8801:在数据表中 https://www.ti.com/lit/gpn/dac8801 SLAS403B

-在第9页上,时序图(图19)显示了15个而不是14个时钟(数据位 D13到 D0和另一个未标记的准 D-1位)。

但是、根据说明、只有最后14位有效、因此 D-1位会将所有发送的数据位向左移动1位、即省略 D13、D12变为 D13等。 D-1变成 D0、因此发送的数据字将完全错误地传输、进而导致不正确的输出值。 用一个包含16个数据位的示例可能很有用、其中前2位无效、如表1下的脚注(1)所述、D0保持低电平后的 CLK 信号也是如此。

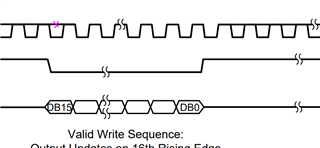

2) 2) DAC8811:在数据表中 https://www.ti.com/lit/gpn/dac8811 SLAS411D

-在第7页上、读取数据位 DB15到 DB0所需的时钟被正确地显示为1到16。 不过、这些边沿实际上会在关闭 CS 信号的同时跟随第17个 L-H 时钟边沿。 情况不应该是这样、因为如果 CLK 信号的评估电子器件比 CS 信号的评估电子器件略快、 读入另一个数据位(D-1)、并且到目前为止读取的所有数据位都向左移动1位、使输出值失真(请参阅1) DAC8801。 这意味着 CS 信号必须提前半个周期变为高电平、甚至在更好的情况下、CLK 信号应在第16个周期后保持高电平。

-在第15页,标题"图24. 数据输入寄存器"的写入方式与往常不同、在上方而不是图片下方会造成混淆。

-在图25 /CS 中断设施图第15页中,所示的 CLK 周期与 Din 数据不匹配: DB15根本没有(有效) CLK 边沿、即发送的第一个位被忽略(DB14变为 DB15)、并且在末尾、缺少第16位并且数据未被接受-即、标为"有效"的第二个写入序列也无效! 至少/CS 信号在时间上已经在 CLK 信号的 H-L 边沿处变为高电平(与3个 DAC 的其他时序图相比)。

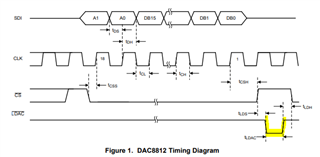

3) DAC8812:在数据表中 https://www.ti.com/lit/gpn/dac8812 SBAS349F

-在第6页上,有效读取数据位(A1、A0、DB15、...、DB0)的 CLK 时钟在时序图(图1)中被错误地标记为18到1,而不是按升序排列的1…18 (参见 DAC8811 1…16)。 与 DAC8811一样、这里还显示了另一个 L-H 时钟边沿、该边沿与 CS 信号变为无效一致。 情况不应如此、因为如果 CLK 信号的评估电子器件比 CS 信号的触摸速度快、 读取另一个数据位(D-1)、到目前为止读取的所有数据位都向左移动1位并伪造输出值(请参阅2) DAC8811)。 这意味着 CS 信号必须提前半个周期变为高电平、甚至更好地在第18个周期后 CLK 信号应保持高电平。

竞争产品 AD5545中已正确显示了这一点。

-在控制逻辑真值表(表2 )的第16页,我发现描述"透明"作为属性的 DAC 寄存器在/LDAC = L 不合适。 DAC 寄存器不是透明的、但仅当/LDAC 处于低电平时、输入寄存器中的数据将传输到 DAC 寄存器、并输出新值。 这就是为什么我认为"更新"一词比"透明"更合适。

为什么上面标记的表和下面标记的图像?

提前感谢、

安东尼