您好!

我的客户使用的是同步模式、使用内部基准电源、输出增益=2。

客户需要分别将值写入 DAC-A 和 DAC-B 并同时输出。 请告诉我如何发送命令。

此致、

西井市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的客户使用的是同步模式、使用内部基准电源、输出增益=2。

客户需要分别将值写入 DAC-A 和 DAC-B 并同时输出。 请告诉我如何发送命令。

此致、

西井市

尊敬的 Nishie-san:

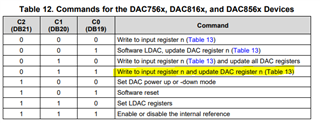

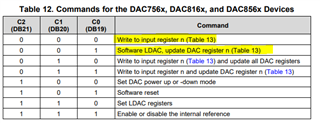

这取决于您是要使用硬件触发器还是软件触发器来更新通道。

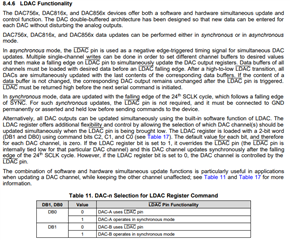

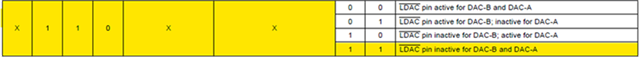

对于硬件触发器、您需要启用 DAC 通道以响应 LDAC 引脚、这是默认操作。 这是在 DB0和 DB1中设置的。

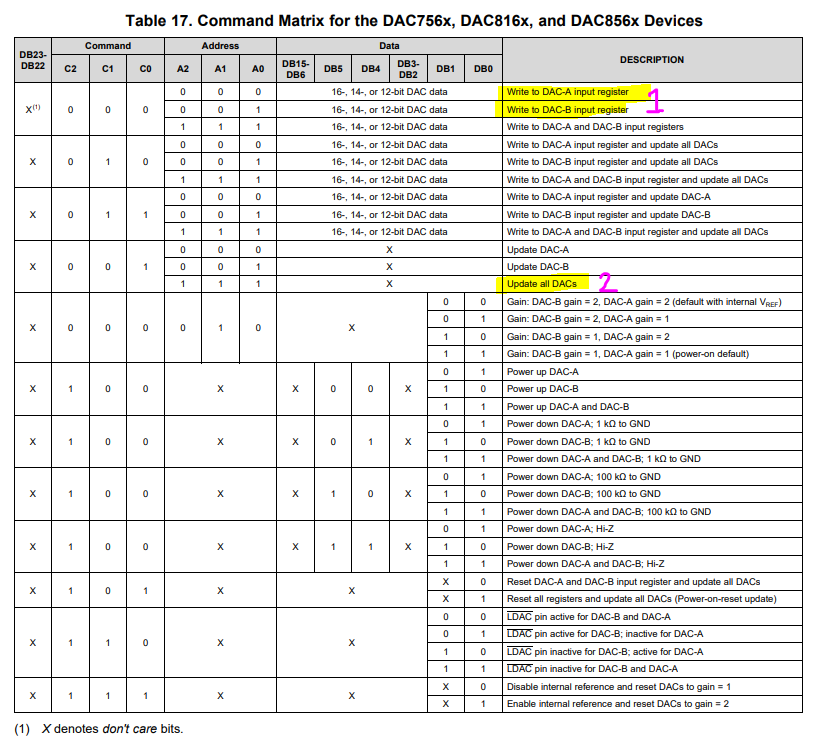

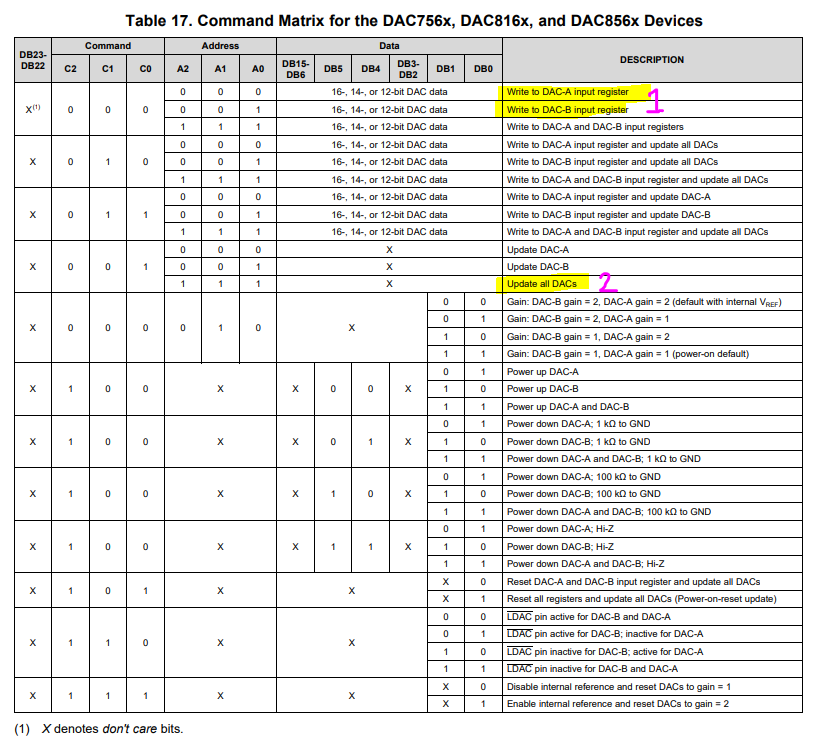

对于软件触发、请将 DB0和 DB1设置为1并保持 LDAC 引脚始终拉低。 首先使用突出显示的命令将输入寄存器更新为每个通道所需的代码、然后使用更新所有 DAC 命令更新两个 OUT

此致!

K·琼斯

尊敬的 Katlynne-San:

感谢您的答复。

因为我使用软件触发器、所以我要设置 DB0和 DB1to1并保持 LDAC 引脚始终拉低。

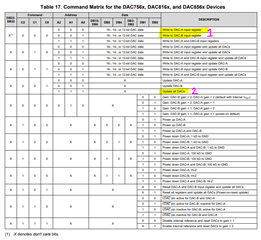

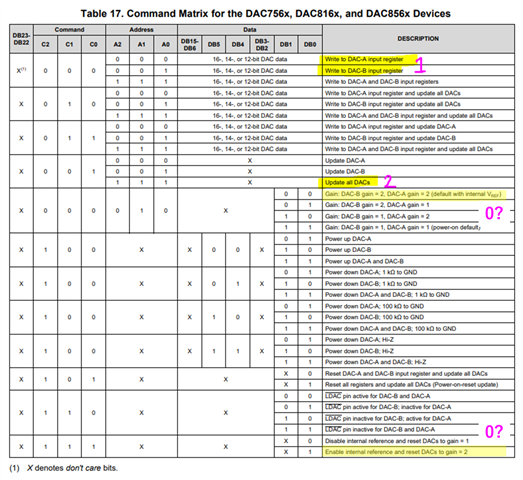

1) 1)应该何时设置"启用内部基准且增益= 2?" (下图0号)

2) 2)还有哪个我要使用"增益:DAC-B 增益=2、DAC-A 增益=2 (内部 VREF 默认设置)"或"启用内部基准并将 DAC 复位为增益=2"?

此致、

西井市

尊敬的 Katlynne-San:

我有两个问题。

我要求客户检查操作、但在下面的过程中、当数字为3时、DAC-A 会输出。 您能否检查一下过程中是否有错误?

1)/始终下拉 LDAC 并发送命令 DB0、DB1=1。

2) DAC 内部基准发送命令以启用电源和双倍输出增益。

3) 3)写入 DAC-A 输入寄存器(下图中的编号1)。

此数据表状态、"当在同步模式中时(/LDAC=Low)、数据在第24个 SCLK 周期的下降边沿上被更新。" 我将这句话解释为:"在同步模式下、一个到输入寄存器输出 DAC 中数据的写入命令。"

如果我使用像将 LDAC 寄存器设置为 DB1/DB0=1/1这样的两步写入操作、即写入输入寄存器(C-2-C0=000)→写入更新寄存器(C2-C0=001等)、是否可以同时输出 DAC-A/B?

此致、

西井市

尊敬的 Nishie-san:

1.0011 0000 0000 0000 0000 0011、DAC-B 和 DAC-A 的 LDAC 引脚未激活

2.0011 1000 0000 0000 0001、 使能内部基准和将 DAC 复位至 GAIN = 2

3. 0000 0000 0000 [0000 0000 0000 0000], 用[]中的数据更新通道 A 输入寄存器

4. 0000 0001 [0000 0000 0000],更新通道 B 输入寄存器 中的数据

5. 0000 1111 0000 0000 0000 0000, 更新 DAC A 和 B 输出

您能否确认他们使用的是上述顺序、并且他们的代码与我分享的代码相匹配?

如果存在应导致 DAC 输出发生变化的某些外部激励源、则通常使用外部硬件 LDAC。 这比使用软件编写更新要快得多。 该命令在 LDAC 被拉至低电平时生效。 这意味着 命令(用于设置和更新 DAC 输出)可以更早地写入、 但 直到外部 LDAC 拉至低电平后才会生效。

在同步模式中、命令将在第24个 SCLK 上生效。 因此该命令在被写入 DAC 后立即生效。 如果您希望输出同时更新、此模式要求您写入输入寄存器、然后更新 DAC 寄存器) "更新所有 DAC"命令实际上是一个软件 LDAC。

此致!

卡琳恩

尊敬的 Erin-San:

感谢您提供的信息。

尊敬的 Katlynne-San:

我还有其他问题。 如果您能回答并申请朋友、我将不胜感激。

由于访问次数减少、客户采用以下 序列进行写入:

*不确定部分是用1而不是0执行的。 nLDAC 引脚连接固定为低电平、因为它与 GND 相连。

它与你告诉我的程序不同、但操作是否有任何不同? (我知道"写入 DAC-B 输入寄存器和所有更新 DAC "和"更新所有 DAC "是相同的、实际上是不同的吗?)

在客户序列中、第三步仅打印了 DAC-A。

此致、

西井市

尊敬的 Nishie-san:

这与您告诉我的程序不同,但操作是否有任何区别? (我知道"写入 DAC-B 输入寄存器和所有更新 DAC "和"更新所有 DAC "是相同的、实际上是不同的吗?)

这两个命令都应将数据从 DAC A/B 移动到 DAC A/B 的输出。 "写入 DAC-B 输入寄存器和所有更新 DAC " 将在更新 DAC B 输出之前更新 DAC B 寄存器中的数据。

在客户序列中,第三步仅打印了 DAC-A。

您是说 DAC A 输出在第三步后发生了变化吗?

客户正在执行的较短顺序应与我之前分享的顺序相同。 它们将我的程序中的步骤4和5合并为两个步骤、它们应该操作相同。

此致!

K·琼斯

尊敬的 Katlynne-San:

我确信设置正确,且示波器屏幕截图显示正确。

客户不希望出现波形般的行为。 私有消息附加的图表显示了执行"写入 DAC-A 输入寄存器"时的波形。 客户希望执行"写入 DAC-A 输入寄存器"、但不想从 DAC-A 输出。 您告诉我的程序是否与客户期望的行为不同?

如果客户还想发送示波器屏幕截图来验证命令1和2,则我可以在等待 EVM 时查看这些示波器。 [/报价]我希望您通过所有方式测量波形。

此致、

西井市

尊敬的 Katlynne-San:

我应在周一获得测试结果以验证同时更新 DAC A 和 B 所需的命令。 [/报价]感谢您的支持。

我期待看到测试结果。

您是否要求我测试此表中 DB0和 DB1的每种组合以验证其是否准确?->否。 我对没有解释表示歉意。

我想检查我描述的四种类型对于 DAC-A/B 输出时序控制方法是否正确。

此致、

西井市

[/quote]

尊敬的 Nishie-san:

我发现程序有问题。 LDAC 引脚应从外部保持高电平、而不是低电平。 在这种情况下、写入输入寄存器的命令不会更新输出、因为它正在等待 LDAC 脉冲。 更新全部 DAC 命令充当 SW LDAC、无需通过硬件更改 LDAC 引脚的状态即可更新输出。

此过程应更新为:

保持 LDAC 引脚始终被拉为高电平

或客户提供的较短版本:

保持 LDAC 引脚始终被拉为高电平

我在 EVM 上确认了这两个过程。

LDAC 寄存器中的 DB0/1确定 LDAC 引脚正常工作还是内部接地。 如果 LDAC 引脚通过 DB0/1在外部或内部接地、则器件将始终在同步模式下工作、"写入 DACx 输入寄存器"将立即更新 DAC 输出。

此致!

K·琼斯