Other Parts Discussed in Thread: DAC3174

您好!

我设计了一个具有8个 DAC3174 DAC 的 PCB、并且希望用简单的设置来测试我的 PCB。

我将 FPGA 设置为12位、并且有两个寄存器(例如 MEMORY_I 和 MEMORY_Q、每个都具有100x12数据)。 我可以将这些数据以循环方式流至 DAC。

我正在使用 FPGA 的 DDR (双倍数据速率)功能、它看起来像这样(来自7系列 FPGA SelectIO 资源用户指南(UG471)):

最终、这些数据会被转换(单端-> LVDS)。 我在调试卡上对其进行了测试、运行正常。

对于 DAC、这意味着我必须对 D2使用时钟上升沿(在本例中为 Q-part)、而对 D1使用下降沿(在本例中为 I-part)。

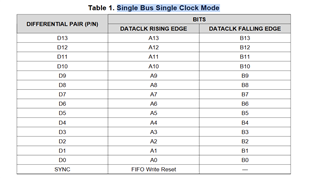

我查看了数据表、发现最适合我的选项是使用"单总线单时钟模式":

我会同时流式传输所有数据、因此还需要同时设置 SYNC 信号是否正确?

我没有找到特殊的寄存器、我必须写入这些寄存器才能激活"单总线"或"单时钟模式"。 我只找到了关于"双总线"的东西。 此模式在寄存器复位后是否开启?

首先、我按照建议使用以下内容启动电路板:

% DACCONFIG:Bit0 -> Resetb、Bit1 -> Alarm、Bit2 -> Ex_ENA、Bit3 -> Sleep

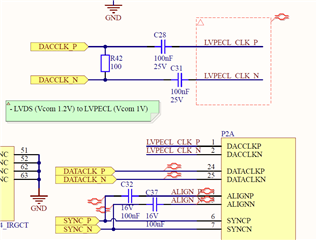

我的主要问题是同步模式。 板上没有足够的空间、因此我使用了相同的行进行同步和对齐。

SYNC 线路处于交流耦合状态并馈送到 ALGIN。 因为 ALIGN 使用 LVPECL、SYNC 使用 LVDS。 我将 SNYC 端口的内部100 Ω 电阻器用作终端。

主要问题是:此设置是否适用于正常双同步?

或者在这种情况下我是否必须使用 SYNC_ONLY?

然后、我写入以下寄存器:

您如何看待此设置?

非常感谢任何帮助!