Other Parts Discussed in Thread: DAC38RF82

主题中讨论的其他器件:DAC38RF82

您好!

我正在使用评估板和信号发生器评估 DAC38RF82。

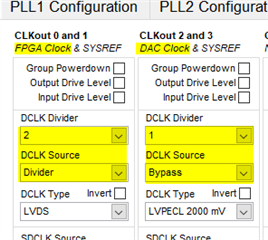

100 MHz /+6dBm 信号馈送到 LMK (J4连接器)的输入端。

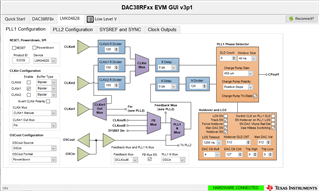

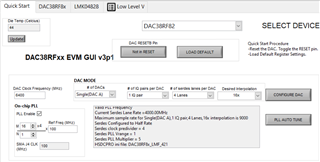

通过以下配置(仅一个 DAC)、一切都正确、DAC 的输出端会存在正确的频谱。

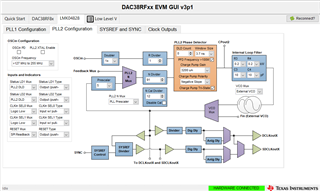

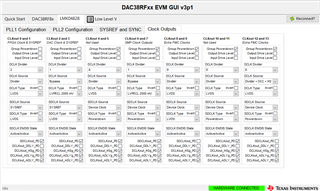

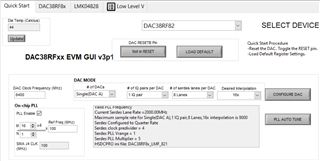

当配置更改为8个通道(而不是4个通道)时,串行器/解串器通道速率降低了两倍,除了 HSDCPRO 文件(后缀821而不是421),没有其他配置更改:

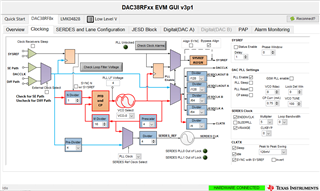

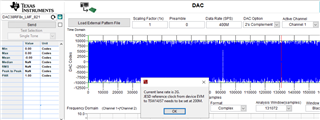

在 HSDCPRO GUI 上,加载正确的 ini 文件(后缀:821)时,将显示以下弹出消息:

重置 DAC JESD 内核(DAC GUI)后、无法在 DAC 输出端检测到频谱(完全无信号)。

我想这是由于 JESD 基准时钟(到 TSW14J57)、必须将其设置为200 MHz (而不是100 MHz)。

此配置有什么问题?