Other Parts Discussed in Thread: ADC3643EVM, ADC3643

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC3643EVM 主题中讨论的其他器件: ADC3643

您好!

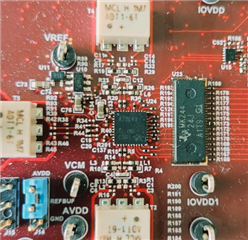

我正在将 ADC3643EVM REV E 与 ZC702 EVM 电路板一起使用、在这种情况下、我想使用 FPGA_CLK 而不是 ADC 的内部时钟。

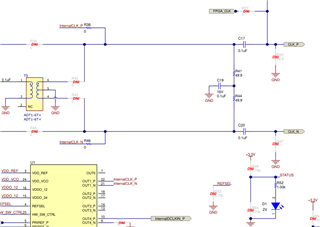

继我的上一篇文章(e2e.ti.com/.../adc3643evm-isue-with-dclk)之后、我了解我必须连接 R37和 R47、并解开 R38、R46、C17、C20、C19、 R41、R44。

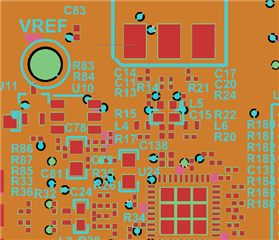

通过查阅站点上提供的光绘文件、我找到了这些组件的位置、但它与我的电路板并不对应。

是否可以使用与 ADC3643 EVM 的 REV E 版本相对应的光绘文件来确定需要焊接和拆卸的元件?

谢谢