您好!

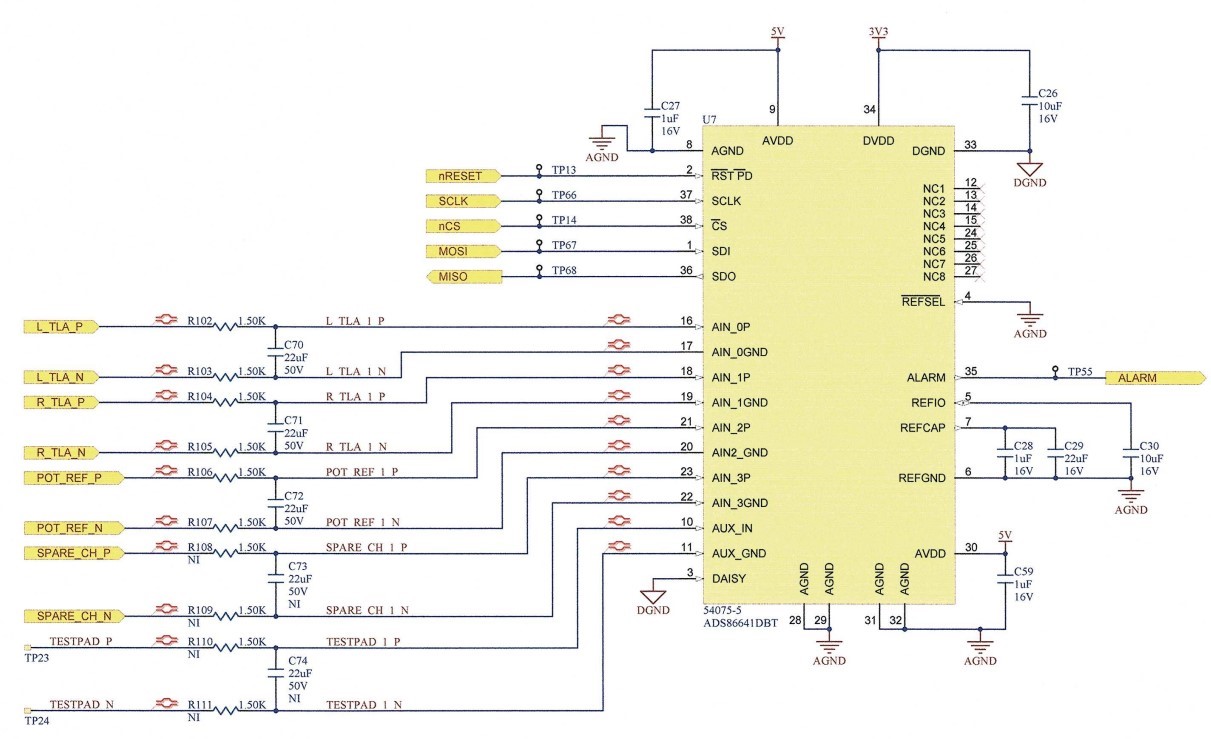

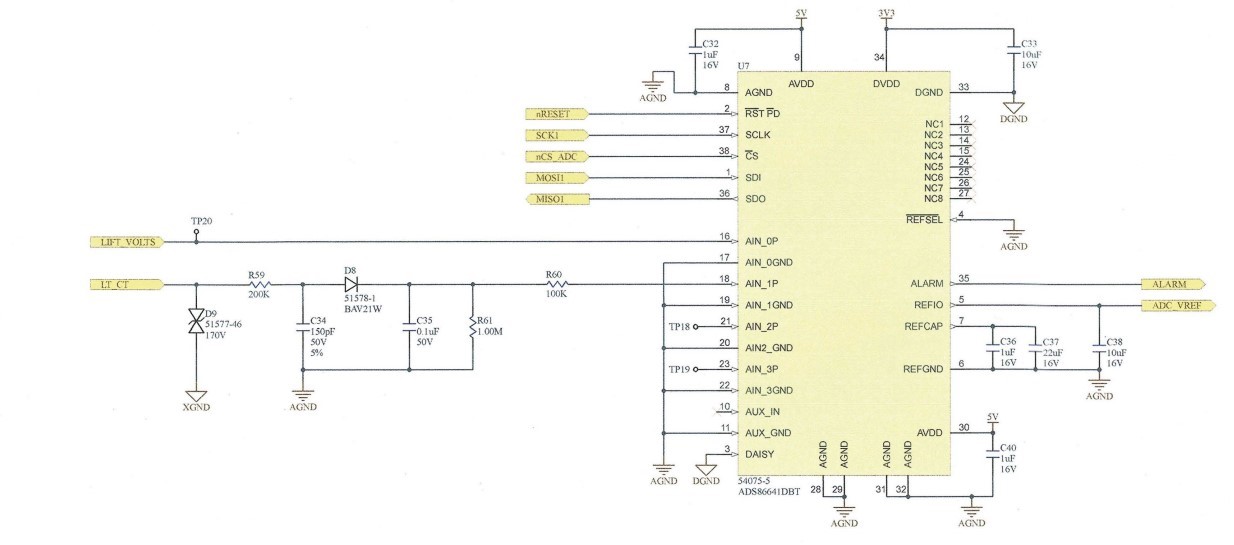

我正在我的其中一个设计中对4个模拟输入信号使用 ADS8664 (原理图如下)。 我遇到的问题是 ADC 输入间歇性锁定。 我已检查 SPI 输出以确保接收微控制器不是器件被锁定、当使用逻辑分析仪时、我可以看到 SPI 消息运行正常、确实重复输出相同的消息。 这意味着 ADS8664会以某种方式在内部"卡住"。

错误有时会通过重启来清除、虽然不一致;当我断开连接到装置的主线束接头时、这一点会更加一致。 在单元运行时、错误已自行清除、但这种情况很少见。 输入的电压范围大约为-10V 至10V。 我们在其他两种设计中使用了此器件、具有完全相同的支持元件并且没有问题。唯一的区别是我们在其他设计中将 REFSEL 接地到 AGND 平面(模拟接地部分)。 如下图所示、我将此芯片接地到了 DGND 平面(数字接地部分)。 数据表中规定"为了选择内部基准、REFSEL 引脚必须连接至低电平或连接至 AGND。" 这条"OR"语句很难理解、因为绑定的低电平可能意味着 DGND。 无论如何、我都曾尝试在出现噪声问题时提起 REFSEL 引脚并将其跳接至 AGND、但问题仍然存在; 但是、如果问题是数字/模拟噪声影响内部电路的另一侧、我不确定速度线是否能有效地完成此类返工。

此问题以相同的方式显示在多个器件上、因此、除非这是"芯片批次"故障问题、否则我已证明、仅更换芯片并不能解决此问题。 我对芯片本身的故障排除没有太多想法、想知道是否要开始调查电路板的其它方面。 我还想知道在此阶段、如果电路外观良好、我可以开始推动软件团队从编程角度进行故障排除、可能是因为时序问题? 该区域超出了我的范围。

如果您有任何建议可以帮助我找到解决方案、我们将不胜感激。

感谢您的观看!