大家好!

我正在尝试使用测试模式来验证 AFE 的输出。 我想通过 ILA 检查输出数据、时钟如下所示:ILA clock = 280MHz AFE input clock = 10MHz 它已设置为14bit 1X 串行化。

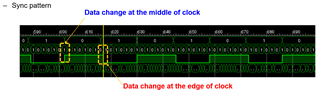

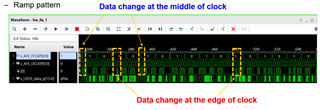

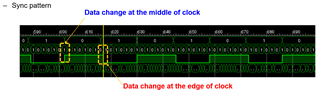

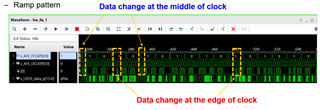

在切换模式中、正如数据表中、我们可以看到数据在 DCLK 的中心发生变化。 然而、在 RAMP 和 SYNC 中、观察到一些数据在 DCLK 边沿发生变化。 潜在的问题和解决方案是什么?

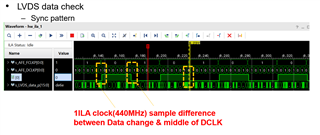

1)同步模式 (工作错误)

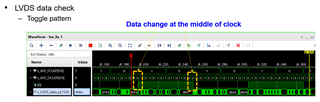

2)切换模式(效果良好)

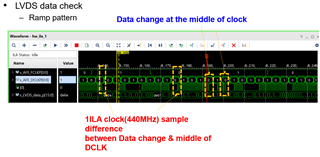

3)斜坡模式 (工作错误)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好!

我正在尝试使用测试模式来验证 AFE 的输出。 我想通过 ILA 检查输出数据、时钟如下所示:ILA clock = 280MHz AFE input clock = 10MHz 它已设置为14bit 1X 串行化。

在切换模式中、正如数据表中、我们可以看到数据在 DCLK 的中心发生变化。 然而、在 RAMP 和 SYNC 中、观察到一些数据在 DCLK 边沿发生变化。 潜在的问题和解决方案是什么?

1)同步模式 (工作错误)

2)切换模式(效果良好)

3)斜坡模式 (工作错误)

您好、我根据您告诉我的更改再次进行了尝试

为便于国际法协会 决议,

FCLK = 7.85714MHz

DCLK = 55MHz ( 14位1X 串行化。)

ILA = 440MHz

不过、测试图形之间仍然存在差异。

借助更好的 ILA 分辨率、斜坡模式和同步模式中仍然存在时序错误。

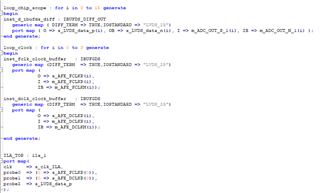

这是我的关于 LVDS 代码和 ILA 的 VHDL 代码。

是否有什么问题导致这种差异?