大家好、

我们将在外部基准模式下使用 DAC80502。

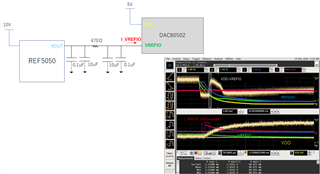

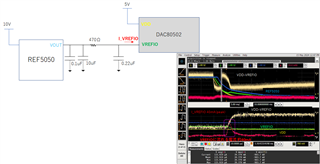

关闭电源后、电压会按 VDD 和 VREFIO 的顺序下降。

此时、电流从 VREFIO 引脚通过 ESD 保护二极管流向 VDD 引脚、但使用限流电阻器将其抑制到10mA 或更低。

然而、当 VDD 引脚电压下降至大约2V 时、大约100mA 的峰值电流将流动。 即使 VREFIO 引脚的电容降至0.22uF、也会产生约40mA 的峰值电流。

该峰值电流是否会影响 IC 的可靠性?

它是否违反数据表中10mA 的输入电流额定值?

此致、