主题中讨论的其他器件:LMK04828、 LMX2594、 LMK61E2、LMK00304

我有关于 ADCxxDJxx00RF 评估模块用户指南的一些问题(修订版 B)

用户指南 ts:https://www.ti.com/jp/lit/ug/slau640b/slau640b.pdf?URL=1716456114996&ref_url=https%253A%252F%252Fwww.ti.com%252Ftool%252Fja-jp%252FADC12DJ5200RFEVM

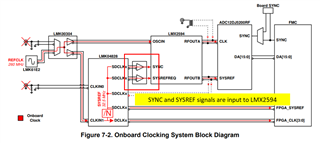

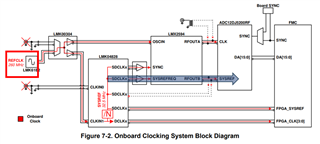

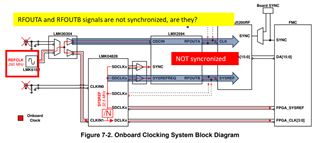

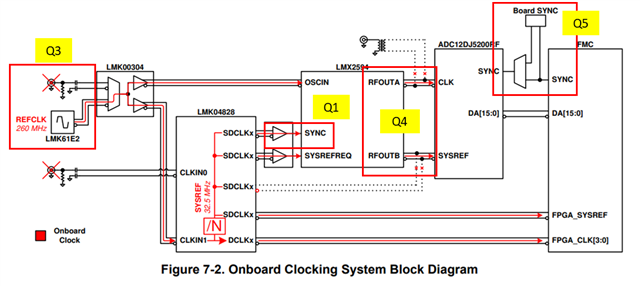

问题1。 我认为从 LMK04828到 LMX2594的 SYNC 信号输入用于对齐多个 LMX2594器件的输出信号。 (图7-2)

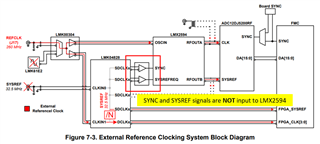

在 EVM 图中、只有一个 LMX2594、因此无需输入 SYNC 信号、对吧?

问题2: 使用板载时钟系统时(图7-2)、SYNC 信号和 SYSREFREQ 信号从 LMK04828输入到 LMX2594。

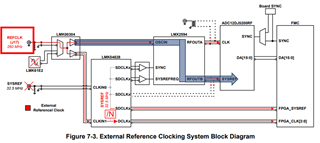

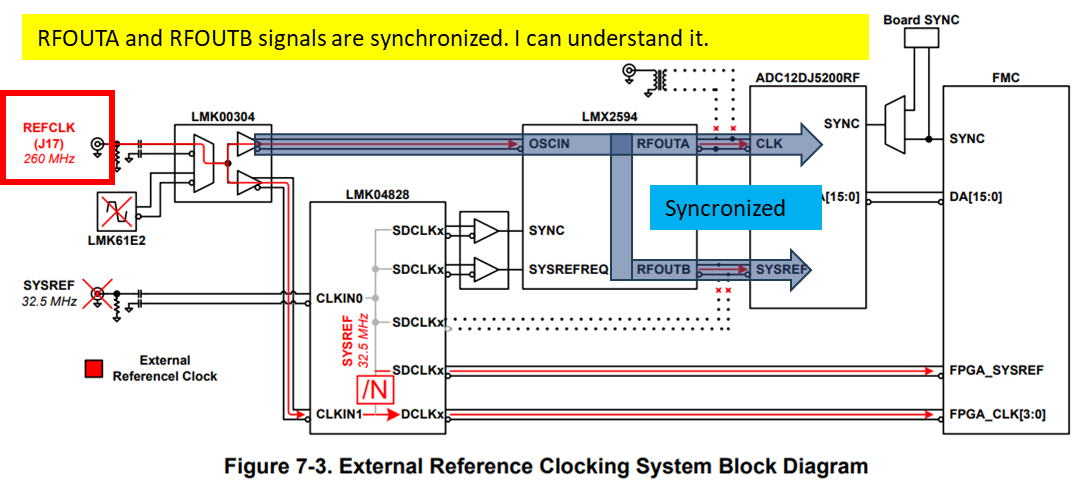

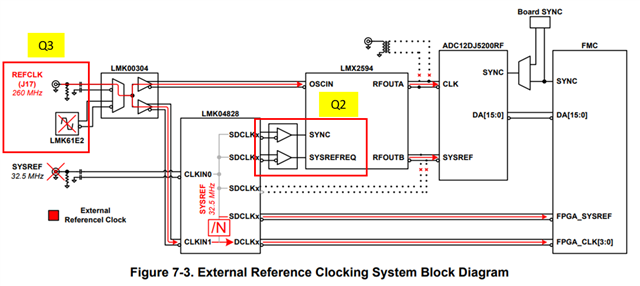

但是、为什么 SYNC 和 REFSYSREQ 信号不在外部基准时钟系统中输入(图7-3)?

问题3。 为什么 SYSREF 的原点仅通过更改输入源而变化?

问题4。 我认为 LMX2594输出 RFOUTA 和 RFOUTB 需要同步。

外部参考时钟系统被满足、这是因为 RFOUTA 和 RFOUTB 由 OSCIN 生成。

板载时钟系统如何同步?

问题5. 什么是板同步?

它与 JESD204的 RX 侧发送的 SYNC~是否不同?