主题中讨论的其他器件: ADS7841

工具与软件:

您好!

我 目前使用的是 ADS7481-Q1 EVM (BOOSTXL-ADS7841-Q1) 、并且在获取准确的 ADC 值时遇到一些困难。

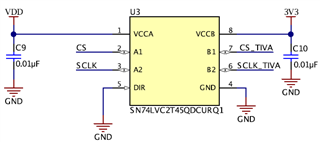

将 BOOSTXL-ADS7841-Q1与 IO 电压电平为3.3V 的应用 FPGA 连接、并连接连接器 J1或 J2上的所有信号线(SPI 线路、SHDN 等)。 VDD 和3.3V 电源引脚电压为3.3V、无需进行电平转换。

尽管遵循了文档中提供的指南和规范、但我们获得的值与预期结果不一致。

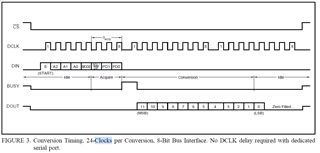

数据表中进行24次时钟转换时的预期信号:

以下是我们观察到的问题的具体详细信息:

- 当 CS 在第24个 时钟周期后变为高电平时、BUSY 信号不变为高电平。

- 根据数据表中给出的图形、在数据发送到 ADC 后(在第8个时钟之后)、BUSY 应该为高电平、但在图中、根据数据表、BUSY 线在第8个时钟之后不会变为高电平。

- 我们在 SDO 线路上没有获得预期的 ADC 值、但它有波动。

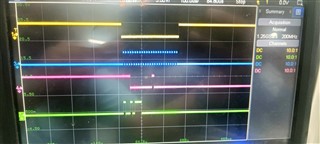

当我们将 ADS7481-Q1 EVM 与 CAN FDL FPGA 连接时、我们在信号线上观察到以下波形:

1.颜色代码:黄色->芯片选择(CS)、蓝色->时钟、紫色->繁忙信号、绿色-> SDI (至 ADC)

2. 色码:黄色->芯片选择、蓝色->时钟、紫色->繁忙信号、绿色-> SDO (来自 ADC)

(由于 DSO 通道限制、上图显示的 SDO 信号与同一 CS、CLK、BUSY 相同。)

CS、SDI、SDO、SCK、BUSY 信号的正确顺序应该是什么?

为了使 ADC 正常工作、我们必须尝试有什么不同吗?

非常感谢!

BR、

Vaibhav