工具与软件:

您好!

I under stand、LMK 可 在分配模式下接受高达3GHz 的 clkin1 IN 引脚。

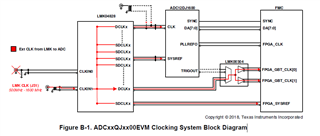

我希望根据下图设计一个系统(图 B-1. SLAU808.pdf 中的 ADCxxQJxx00EVM 时钟系统方框图)

- LMK clkin1的输入时钟为1GHz。

- DCLK 输出到 ADC 时钟也1GHz =采样率

- JMODE8中的 ADC = 4个通道/12位/64/66 = 12.375Gbps 的通道速率

-根据 ADC 数据表 TRIG OUT 将是386.71875MHz (通道速率/32或可能是/64)可选择用于 FPGA GBT 时钟。

-鉴于以上所有情况,我需要知道 LMK 在进入 FPGA GBT 时钟的输出端产生的频率是多少?

此致、

Giora