Other Parts Discussed in Thread: DAC39RF10EVM, LMX1204

主题中讨论的其他器件: LMX1204

工具与软件:

尊敬的 TI:

我将使用 DAC39RF10EVM 和 HSDC Pro 生成单音信号(DEM/抖动均启用)、采样率 Fs 为1GHz、输入频率 fin 范围为0至 Fs/2。

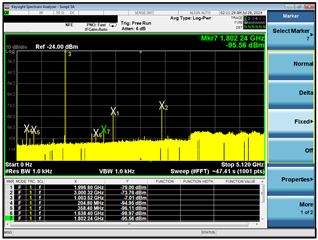

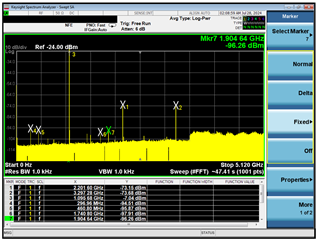

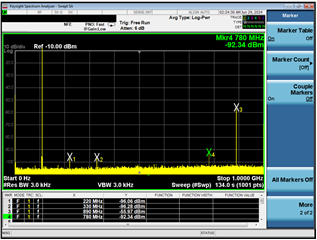

但我在特定频率上发现了一些意外杂散、这些杂散通常在输出频谱中等间隔、例如当我设置 fin = 60MHz 和70MHz 时、输出频谱为:

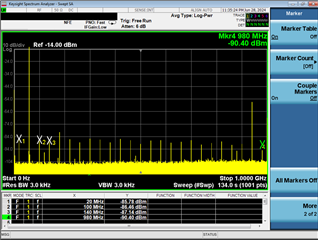

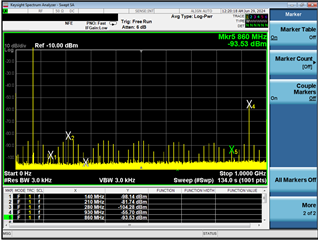

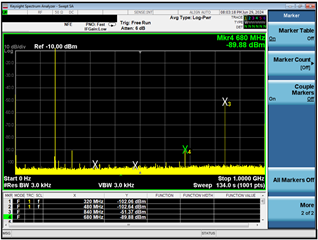

但是,当我设置其他输入频率(例如 fin = 110MHz、160MHz )时,没有这样的杂散:

我想知道这些杂散的原因是什么、对如何解决这些杂散有什么建议吗? 我也 在论坛中找到了类似的问题、但没有指出杂散的来源: DAC38J84:杂散问题-数据转换器论坛-数据转换器- TI E2E 支持论坛。

以下是我的 DAC39RF10EVM GUI 配置:

谢谢,期待您的答复。