工具与软件:

您好、简单来说、我想在低分辨率模式下使用 ADC。

从数据表中我了解到、帧由 CS 分隔、但帧长度必须为16个时钟周期:

"串行帧在 CS 的下降沿启动、在 CS 的上升沿结束。 每个帧必须包含16个 SCLK 上升沿的整数倍。"

但从以下句子中看、对于控制寄存器而言、仅8个时钟周期就足够了:

"在每次转换期间、数据在 CS 下降后、通过 SCLK 前8个上升沿上的 DIN 引脚在时钟控制寄存器中。"

如果我不需要完整的 ADC 分辨率、可以使用 CS 提前结束转换吗?

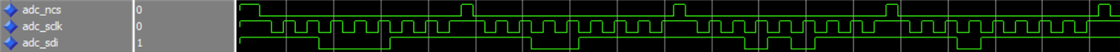

也就是说、我可以像下面时序图中那样使用 ADC 吗? 在这里、我只使用8个时钟周期、因此我将使用4个输出位作为示例。 SDI 和 SCLK 具有高空闲状态。

例如、如果我的 SCLK 频率为800kHz、我使用4个通道、分辨率为8位(12个 SCLK 周期+ 1个 CS 周期)、这是否意味着我的转换频率 为61.538kHz、我的采样频率为每通道15.384kHz?

此致