主题中讨论的其他器件: LMK04828

工具与软件:

您好!

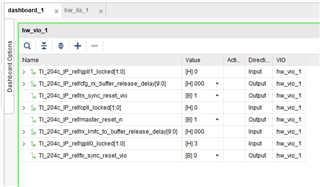

我使用 TI204C-IP 为 DAC38J82运行示例。

我从 DAC38J82获得的寄存器值从0x64到0x6C。 下面是该值。

寄存器0x64 = 0

寄存器0x65 = 0

寄存器0x66 = 0

寄存器0x67 = 0

寄存器0x68 = 0

寄存器0x69 = 0

寄存器0x6A = 0

寄存器0x6B = 0

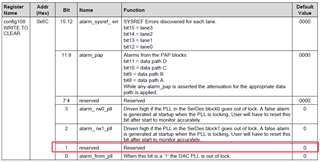

寄存器0x6C = 0x3 (旁路 DAC PLL)

我有2个问题。

问题1:从数据表中、 寄存器0x6C 位1被保留、应该为0、但我得到了1。 是否正常?

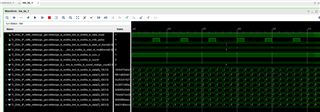

问题2:从寄存器值来看、在上拉 TXEN 后、DAC 似乎正常工作、但我看不到来自输出 A+的波形。 是否还有其他可能?

谢谢

此致

Daniel