Other Parts Discussed in Thread: ADC3662EVM

工具与软件:

您好!

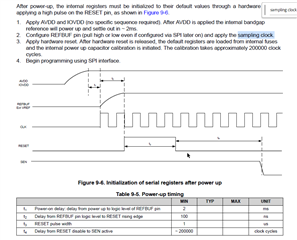

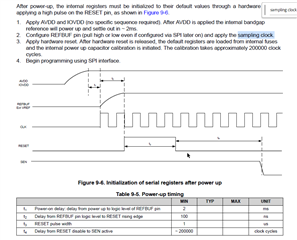

数据表规定、REFBUF 引脚应向 AVDD 延迟2ms:

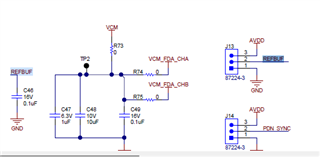

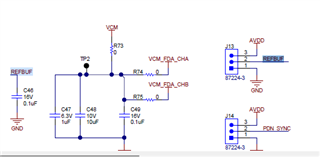

在 ADC3662EVM 原理图中、REFBUF 引脚通过跳线直接连接到 AVDD:

所以,在我看来,没有包括延迟! 该延迟是否真的很必要、或者只是如果您使用内部电压基准呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADC3662EVM

工具与软件:

您好!

数据表规定、REFBUF 引脚应向 AVDD 延迟2ms:

在 ADC3662EVM 原理图中、REFBUF 引脚通过跳线直接连接到 AVDD:

所以,在我看来,没有包括延迟! 该延迟是否真的很必要、或者只是如果您使用内部电压基准呢?

您好、Simon:

很抱歉耽误您的时间、感谢您指出这一点。

我们计划将该表添加到下一版本的数据表中。

我们在 EVM 上没有发现任何问题。

此致、

Rob

|

REFBUF 电压 |

ADC 模式 |

上电时序 |

提供反馈意见 |

复位时序 |

|

0 V/接地 |

用于单端时钟、内部基准 |

无需时序 |

|

VDDA 上电后2ms |

|

悬空 |

对于外部基准、请使用差分时钟 |

无需时序 |

|

VDDA 上电后2ms |

|

1.8V |

对于外部基准、请使用差分时钟 |

与 VDDA 相同上电或连接到 VDDA |

|

VDDA 上电后2ms |

|

约为0.6V |

内部参考时钟为差分时钟 |

在 VDDA 的同时上电 |

即使它是在 VDDA 之前或 VDDA 之后的某个时间设置、也不会出现问题 |

VDDA 上电后2ms |

|

确切值为1.2V |

外部基准、差分时钟、外部带隙 |

与 VDDA 相同上电 |

即使它在 VDDA 之前设置也不会出现问题;在 VDDA 之后对其上电不安全、因为它会使外部基准和内部基准短路 |

VDDA 上电后2ms 或 REFBUF 引脚上电后2ms、以较晚者为准 |