工具与软件:

当 MCU 与 ADS131B04 SPI 通信时、通过示波器观察到 DRDY 信号在 SPI 时序中主要保持在低电平、当有数据传输时将发生跳变、这是否正确? 因为我看到写入数据表中的 DRDY 看起来始终为高电平、从而在数据就绪时提供下降沿

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

当 MCU 与 ADS131B04 SPI 通信时、通过示波器观察到 DRDY 信号在 SPI 时序中主要保持在低电平、当有数据传输时将发生跳变、这是否正确? 因为我看到写入数据表中的 DRDY 看起来始终为高电平、从而在数据就绪时提供下降沿

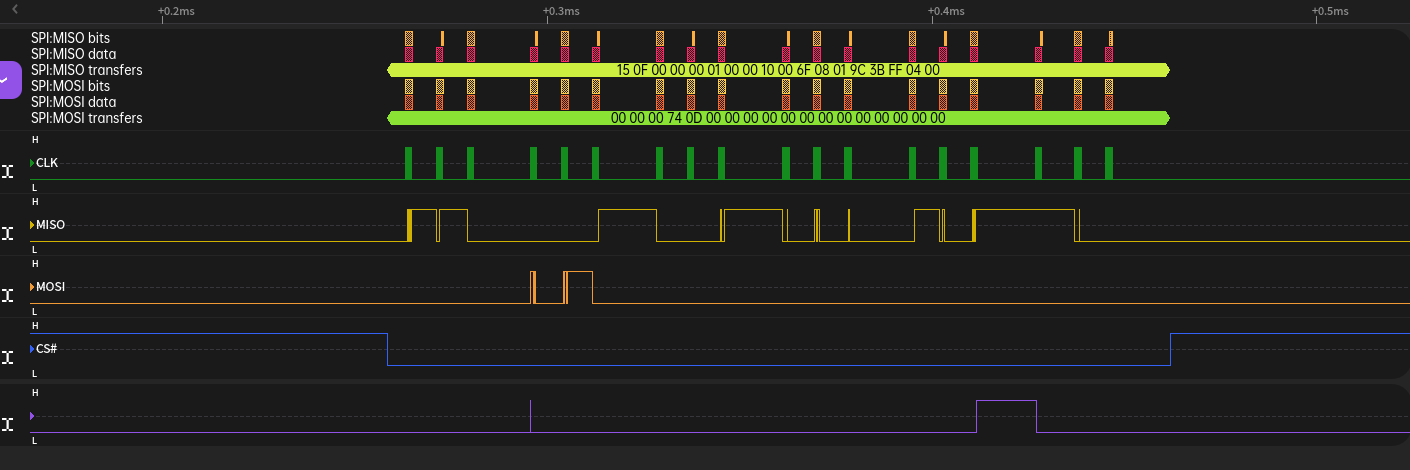

1、(CLKIN 设置为8kHz)异常 DRDY 行为仍会获取正确的数据、程序内读取数据行为由 DRDY 引脚上的外部中断触发。 当我运行命令以每10ms 在循环中读取一次数据时、示波器会显示如上图所示的异常、只有当周期设置为大约8ms 时、我才能获得正常的 DRDY 行为、DRDY 周期大约为9ms。 我想知道为什么

2、当我禁用输入 crc,为什么 sendcommand ()和 writesingleresgister ()行为正常,但我无法获取数据,并且始终显示0x2020。

3 μ s、全局斩波模式时、您只需照常读取数据、因为我多次阅读手册中记录的类似数据均值计算行为、存在 t (GC_CONVERSITION)周期时间、您能详细介绍一下运行全局斩波模式的情况吗

您好? ?、

您是否有逻辑分析仪而不是示波器? 我想同时查看所有数字信号(SCLK、CS、DRDY、DOUT、DIN)。 我也看不到你的图像上的时间刻度,所以我不能真正告诉正在发生什么

您展示的图像似乎需要很长时间才能按时钟输出所有数据。 这就是 DRDY 在该帧的大部分时间内保持低电平的原因。 这也是逻辑分析仪有用的原因、因此我可以看到与 ADC 之间的所有通信

请提供逻辑分析仪数据、以便我们进一步为您提供帮助

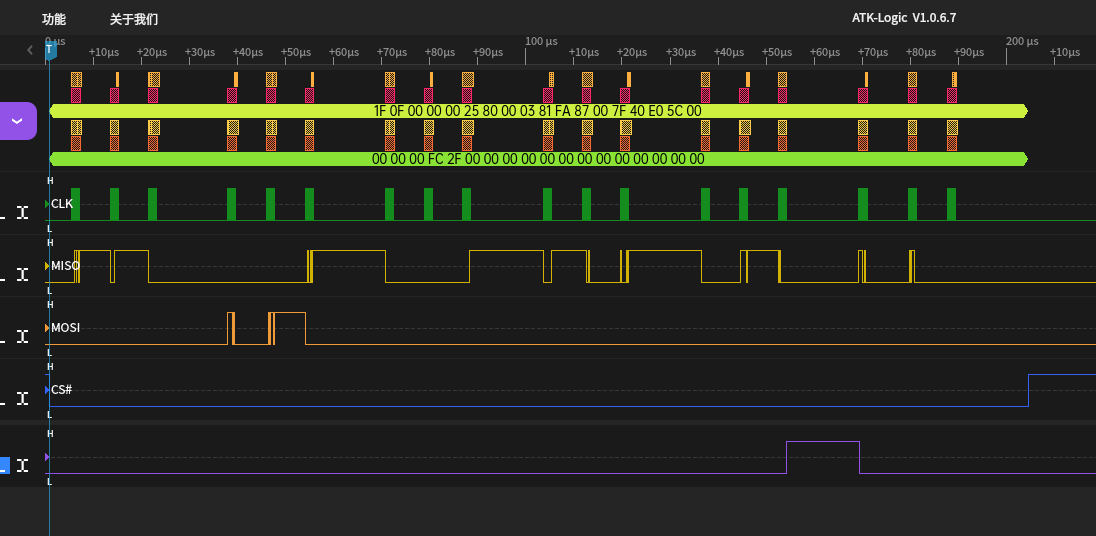

-Bryan

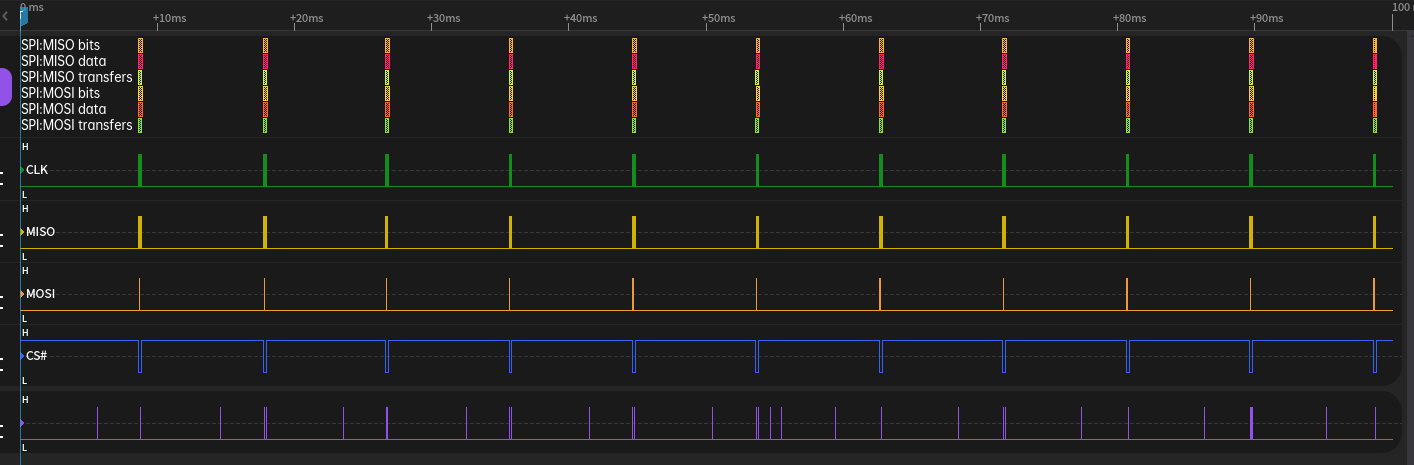

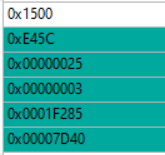

第一是一个通信信息序列、DRDY 是一条紫线、在图中可以看到 DRDY 始终保持低电平、在读出数据后变为高电平、但时间非常短、因而引入了下降沿。 图2中显示了更广泛的信息。 图3是 MCU 读取的信息、与图4的时序相对应、但可能由于逻辑分析仪的精度、逻辑分析仪可能会显示一些错误。 尽管 DRDY 表现出如图中所示的奇怪行为、但读取的数据仍然正确。 您能帮我解释一下这个现象吗? 此外、I CYCLE 读取数据的时间为10ms、32768当 I 设置 GC_DLY 时、外部时钟选择8MHz 时、这一次两帧之间的间隔约为8ms、因此 SPI 时序的读取与此类似、仅当周期读取数据时间设置为8ms 时、SPI 时序才正确。 但是、既然我仍然需要10ms 的读取时间、那有什么办法吗?