Other Parts Discussed in Thread: ADS127L21

工具与软件:

您好!

我对 ADS127L21有几个问题。

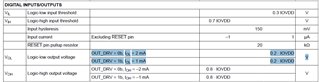

根据上图:

我担心 SDO/DRDY 的最大逻辑低电平输出电压(VOL)。 我读取到最大逻辑低电平输出电压为0.2 x IOVDD。 我的 IOVDD 为5V、因此 VOL (最大逻辑低电平输出电压)将为1V。 是这样吗?

或者、此计算是否特定于来自外部上拉电阻器或电流源的1mA 或2mA 电流?

对于 SDO/DRDY 内部 RDS_ON 电阻计算:

0.2 x 5V = 1V、这意味着在2mA 或1mA 时 VOL_max = 1V、对吧? 我将采用1mA 电流源进行此计算。

SDO/DRDY 内部电阻器将是:1V/DRDY 1mA = 1k Ω 是否正确?

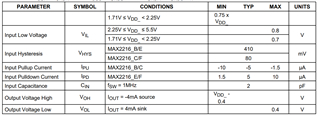

根据上图:

我使用了一个数字隔离器、其上拉电流为5V (5V / 10µA = 500kΩ 上拉电阻器)时的10µA、最大逻辑低电平电压为0.8V。

当 ADC 驱动输出进入低电平状态时、输出电压变为(1kΩ/(500kΩ+ 1kΩ)) x 5V = 0.01V。 那么、输出电压是0.01V、对吧? 我们也可以对输出进行相同的计算吗?

我希望能迅速作出答复。

谢谢你