Thread 中讨论的其他器件: LM25116、 LM5116、LM5088 、LM25088、LMZM33604、 TPSM63608

工具与软件:

尊敬的 TI 团队:

我们正在设计一个要求模拟电压范围为的电路 0至-12V 偏置 256个变容二极管 反向电压区域。 评估这些选项后、我们选择了 DAC61416 这一目的。 但是、我们想澄清一些技术细节:

-

电源要求 :

- 实现的输出范围 0至-12V 请确认的相应值 VCC 、 VSS 、 VDD 和 Vaa ?

-

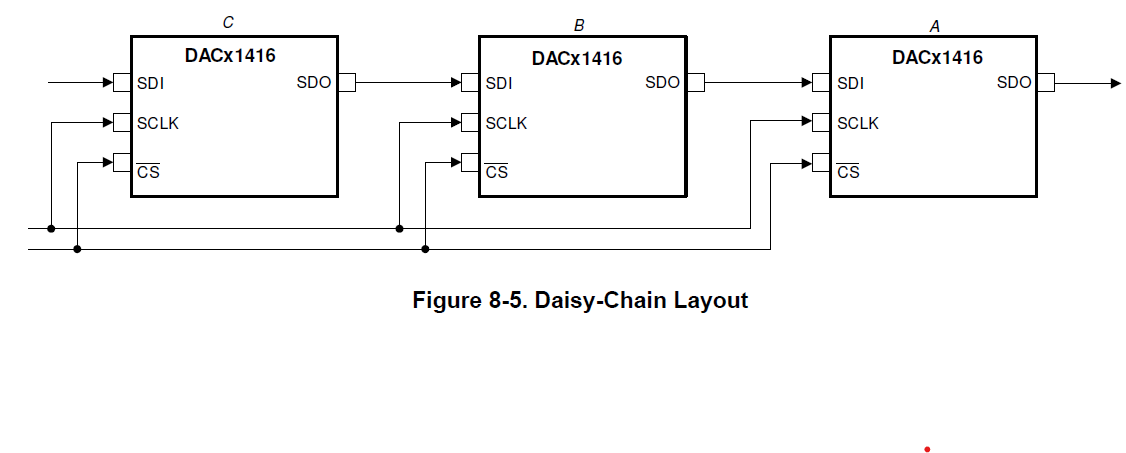

SPI 菊花链 DAC :

- 鉴于我们需要偏置256个变容二极管、我们计划使用 16个 DAC61416器件 . 在与微控制器连接时、您能否提供有关这些 DAC 菊花链 SPI 接口的最佳方法的指导?

-

附加电路 :

- 在将 DAC 输出施加到变容二极管之前、您建议是否使用任何其他电路(例如缓冲器或放大器)来调节 DAC 输出?

附件为我们设计的简图、供您参考。

我们感谢您的支持、并期待您对这些问题的指导。

此致、

Meghla