工具与软件:

亲爱的先生们、

我正在使用 ADC34J45、我有一个与数字化信号相位噪声相关的问题。

ADC34J45的配置如下所示:

-输入频率= 47.4 MHz -20dBm 不调制

(-84dBc 至25KHz 偏移、BW = 25KHz)

- 频率时钟:158.4MHz LVDS 电平大约为0dBm 到 ADC 的输入

(85dBc 相邻通道至25KHz 偏移(BW = 25KHz))

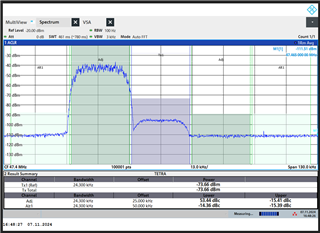

但是、ADC 数字化的信号显示出高相位噪声和非常糟糕的相邻通道

下面是使用 MATLAB 进行分析的数字信号。

放大47.4MHz:

正如您可以检查的那样、与输入信号和时钟信号的相位噪声相比、相位噪声非常糟糕。

我已经检查了将直流滤波器增加到低噪声 LDO 输入的电源、该 LDO 用于为 ADC 提供+1.8AVDD。 我将使用德州仪器(TI)的 TPS7A9101DSK 的 LDO 来实现18AVDD。

请查看随附的一个包含 ADC 样本的文件、其中的值与 ADC 的输出相关乘以4。

e2e.ti.com/.../BufferRxData_5F00_B.txt

最后、ADC 的输入阻抗为200欧姆、因此0dBFS 约为+4dBm。

请帮我理解这个问题吗?

提前感谢。

此致、

佩德罗