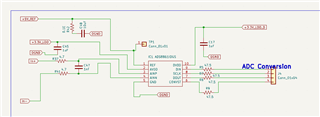

工具与软件:

我将使用 FPGA 获取采样数据。 我正在使用一个3线操作,到目前为止,我已经从数据表中获取了一切。

SCLK:- 25 MHz (40ns)。

转换之间的时间: 远远超过1000ns。

采集时间:- 640 ns。 (远高于最小收购的限制)。

下面是波形。

波形1:底部是凸信号。 中间的是 SCLK。 上面的这个是 Din (恒定高电压为3.3V)。 粉色的一个是要采样的输入波。

波形2:

它显示了转换之间的时间也很好。

Out of the DOUT 是一个恒定的3.3V 高波形。 是否有解决方案?