工具与软件:

我目前正在尝试将 ADC12QJ1600 EVM 与 VCK190一起设置。

设置说明:

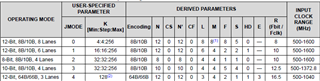

- JMODE4

- 3个通道

- 64B66B 编码

- FS = 1000 MHz

- core_clk = 250 MHz

- 串行器/解串器= 165000 MHz

- 从 LMK 到 ADC 的外部时钟:因此、通过 SMBV100A 将1GHz 直接分配给 ADC

- E = 3

- SYSREF = SERDES /(E*66*32*n)对于 n = 1 --> SYSREF = 2.6041666 MHz

我在 FPGA 上使用了最新的 ADC12QJxx00EVM GUI 版本和 Xilinx JESD204C IP 内核版本7.2。

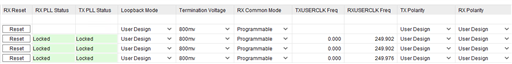

现在可以在 FPGA 上的 JESD IP 内核上捕获 SYSREF、但未实现同步报头锁定状态。

作为参考、我使用 GUI 对 ADC 进行了编程、然后启用了 SYSREF 接收器和 SYSREF 处理。 然后、使用 FPGA 中的 ILAS 对 SYSREF 和 CORE_clk 进行分析、结果是正确的。 此外、内核脱离复位状态和捕获了 SYSREF 这一事实也让我得出这个结论。

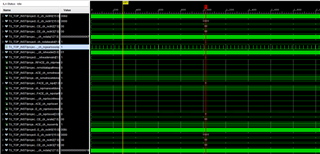

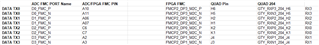

为了测试连接、我尝试在 ADC 上生成 PRBS15测试并使用 Vivado IBERT 捕获数据。 这几乎是可行的。 (请参阅图片)

通道2上的链路无法实现。 在 JESD 内核上未找到同步报头。 我还分析了从四核到 JESD RX 接口的 AXI 流、在标头中看到了许多禁止的标头(例如"11"、"00")。

现在我的问题。 ADC 设置中的问题在哪里、或者我应该重新访问 FPGA 设置?

ADC 中的 JESD_STATUS 寄存器读出

0x208 0x6

- CPLL_LOCKED = 0 (不使用 ADC PLL)

- RES33 = 0

- SERDES_PLL = 1

- 对齐= 1

- REALIGNED = 0

- SYNC_STATUS = 1 (不使用 SYNC)

- LINK_UP = 1

- RES34 = 0

对我来说、一切看起来都很好、它实际上应该能正常工作。 我使用 ADC 的附加配置。

ADC12QJxx00 0x00 0x30 0x02 0x00 0x10 0x00 0x29 0xE0 0x2A 0x00 0x2B 0x15 0x30 0x00 0x31 0xA0 0x37 0x4B 0x3B 0x00 0x3C 0x01 0x3D 0x00 0x3E 0x20 0x3F 0x4F 0x48 0x02 0x50 0x00 0x57 0x00 0x58 0x00 0x59 0x20 0x5C 0x00 0x5D 0x40 0x61 0x01 0x62 0x01 0x65 0x01 0x68 0x61 0x6B 0x00 0x6C 0x01 0x6E 0x88 0x7A 0x7B 0x7C 0x0A 0x7E 0xA9 0x7F 0xAA 0x80 0xA9 0x81 0xA9 0x9D 0x03 0x160 0x00 0x200 0x01 0x201 0x04 0x202 0x1F 0x203 0x01 0x204 0x09 0x205 0x00 0x206 0x00 0x207 0x00 0x208 0x7C 0x209 0x03 0x20F 0x00 0x210 0x03 0x211 0xF2 0x213 0x0F 0x270 0x01 0x29A 0x0F 0x29B 0x04 0x29C 0x1B 0x2C1 0x3F 0x2C2 0x3F 0x2C4 0xFF 0x330 0x8B 0x331 0x08 0x332 0x37 0x333 0x08 0x334 0xF0 0x335 0x07 0x336 0x0F 0x337 0x08 0x338 0x5F 0x339 0x08 0x33A 0x93 0x33B 0x07 0x33C 0x5F 0x33D 0x08 0x33E 0xC7 0x33F 0x07 0x360 0x10 0x361 0x10 0x362 0x13 0x363 0x0F 0x364 0x13 0x365 0x0D 0x366 0x10 0x367 0x10 LMK04828 0x00 0x00 0x02 0x00 0x100 0x01 0x101 0x55 0x103 0x02 0x104 0x20 0x105 0x00 0x106 0xF1 0x107 0x06 0x108 0x01 0x109 0x55 0x10B 0x00 0x10C 0x22 0x10D 0x00 0x10E 0xF0 0x10F 0x60 0x110 0x04 0x111 0x55 0x113 0x00 0x114 0x02 0x115 0x00 0x116 0xF1 0x117 0x01 0x118 0x01 0x119 0x55 0x11B 0x02 0x11C 0x02 0x11D 0x00 0x11E 0xF9 0x11F 0x01 0x120 0x04 0x121 0x55 0x123 0x00 0x124 0x22 0x125 0x00 0x126 0xF1 0x127 0x01 0x128 0x01 0x129 0x55 0x12B 0x02 0x12C 0x22 0x12D 0x00 0x12E 0xF0 0x12F 0x10 0x130 0x01 0x131 0x55 0x133 0x02 0x134 0x22 0x135 0x00 0x136 0xF8 0x137 0x01 0x138 0x45 0x139 0x03 0x13A 0x01 0x13B 0x80 0x13C 0x00 0x13D 0x08 0x13E 0x03 0x13F 0x00 0x140 0x00 0x141 0x00 0x142 0x08 0x143 0x11 0x144 0xFF 0x145 0x00 0x146 0x18 0x147 0x02 0x148 0x02 0x149 0x02 0x14A 0x06 0x14B 0x02 0x14C 0x00 0x14D 0x00 0x14E 0x00 0x14F 0x7F 0x150 0x01 0x151 0x02 0x152 0x00 0x153 0x00 0x154 0x0C 0x155 0x00 0x156 0x0C 0x157 0x00 0x158 0x78 0x159 0x00 0x15A 0x78 0x15B 0xD4 0x15C 0x20 0x15D 0x00 0x15E 0x00 0x15F 0x0B 0x160 0x00 0x161 0x02 0x162 0x44 0x163 0x00 0x164 0x00 0x165 0x0C 0x166 0x00 0x167 0x00 0x168 0x01 0x169 0x59 0x16A 0x20 0x16B 0x00 0x16C 0x00 0x16D 0x00 0x16E 0x04 0x17C 0x15 0x17D 0x33 LM95233 0x03 0x00 0x0C 0x01 0x40 0x55 0x41 0x6E OSC_ENA 0x00 0x00 GBT_SEL 0x00 0x01 PLL_ENA 0x00 0x00 PLLREF_SE 0x00 0x00