工具与软件:

你(们)好

我正与 AFE58JD48EVM 评估板合作、通过 JESD204B 接口将 ADC 数据发送到 FPGA、然后通过 Wavevision 在 JESD204B RX 上绘制提取的数据。

我将在信号发生器的 ADC 输入端发送一个1MHz 400mVpp 方波、而 FPGA 侧捕获的波形对1MHz 具有电容效应、但当我们提高频率时、捕获的波形会改善。 因此、我想知道其原因、是因为输入路径中的电容器、还是与模拟前端仪表有关。 我已将所有测试用例的 LPF 设置保持为60MHz。

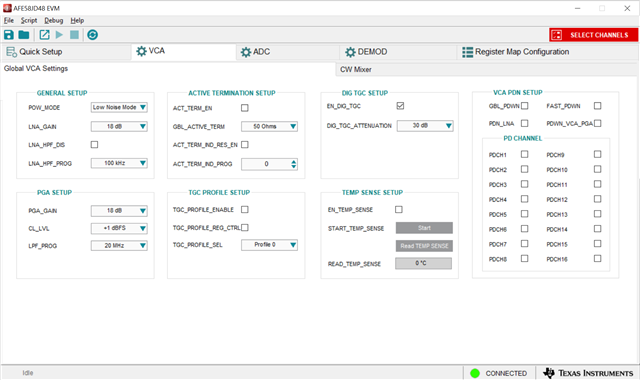

我已经附上捕获的波形和我为大家参考而设置的 VCA 参数。

另外还存在一个疑问、即在电容器之前的 ADC 输入端、我们已经添加了一个49.9 Ω 的并联端接电阻、而且在 ADC 内部还启用了50 Ω 端接、因此这会影响我们的路径、因为这样一来、路径中的有效并联端接将为25 Ω、而不是50 Ω。