工具与软件:

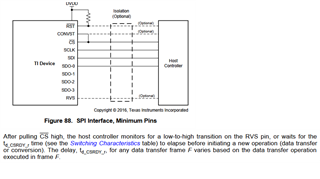

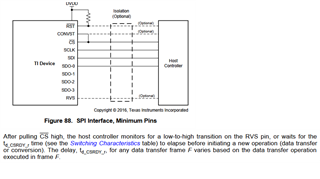

如何使用来自主机控制器的单个信号(驱动 CONVST 和 CS 引脚)以及关于 CS 上升至 RVS 上升时序(TD_CSRDY_r)的最小引脚(如数据表第7.5.5.2节所述)与协调、如第7.5.2节所述: "将 CS 拉为高电平后、主机控制器会监测 RVS 引脚上是否发生从低电平到高电平的转换、或者等待 TD_CSRDY_r 时间(请参阅开关特性表)消失、然后再启动新的操作(数据传输或转换)"?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

如何使用来自主机控制器的单个信号(驱动 CONVST 和 CS 引脚)以及关于 CS 上升至 RVS 上升时序(TD_CSRDY_r)的最小引脚(如数据表第7.5.5.2节所述)与协调、如第7.5.2节所述: "将 CS 拉为高电平后、主机控制器会监测 RVS 引脚上是否发生从低电平到高电平的转换、或者等待 TD_CSRDY_r 时间(请参阅开关特性表)消失、然后再启动新的操作(数据传输或转换)"?

尊敬的 David:

感谢您的提问。 上一篇 E2E 文章我的问题回答: https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/1068570/ads9110-connect-cs-and-convst-together-generating-problems

如果需要其他支持、请告诉我。

此致、

Samiha

Samiha,请花必要的时间阅读以前的帖子的内容,然后再回复,在结束时,您将节省我们两个时间。

是的、TD_CSRDY_r 时间定义为最大规格、但介于 CS RISE 和 RVS RISE 之间。

另一方面、数据表要求我们(请参阅第一个帖子中的随附图像)等待 RVS 上升或 TD_CSRDY_r 时间到期、然后才能启动新的转换。

如果 CS 和 CONVST 由同一信号驱动、则无法做到这一点。

您能解释一下吗?

此致、

David

David、

我理解这种困惑。 我认为问题在于数据表中使用的术语"转换"。 在第7.5.2节中、当数据表显示:

".. 等待 TD_CSRDY_r 时间(请参阅开关特性表)过去后再启动新的操作(数据传输或) 电源转换 )"。

这里、术语"转换"意味着新采集周期的开始。 因此、TD_CSRDY_r 实际上并不是一个可以满足的时序、而是器件的开关特性。 您可以同时将 CONVST 和 CS 升高为高电平、以启动 CONV 状态。 经过 t_cycle 后可能启动下一个 CONV 状态、其中 t_cycle = t_conv_max + t_acq_min (通过再次将 CONVST 和 CS 升高为高电平)。

此致、

Samiha