请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TI-JESD204-IP 工具与软件:

您好!

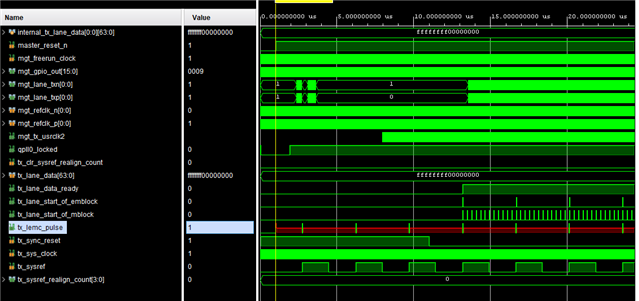

我一直在尝试在 TX 和64b66模式下对 TI JESD204C 进行仿真、但仿真失败时遇到了问题:

- tx_lemc_pulse 脉冲 ,但在脉冲之间不定义

- TX_LANE_START_OF_EMBLOCK 仅每 12个块脉冲一次、即使 PARAM_TX_E 设置为1也是如此。

以下是 IP 的实例化:

TI_204c_IP #(

// IP type and protocol

.IP_TYPE ("TX"),

.IP_PROTOCOL (6466),

// Converter resolution

.ADC_RES (16),

.DAC_RES (16),

// 64b/66b protocol parameters

.PARAM_RX_E (1),

.PARAM_TX_E (1),

// MGT (Transceiver) parameters

.GT_TYPE ("GTHP"),

.NUM_REFCLK_BUFFERS (1),

.NUM_QUADS (1),

.NUM_RX_LANES (1),

.RX_LN_IDX_WIDTH (1),

.RX_LN_DATA_WIDTH (64),

.NUM_TX_LANES (1),

.TX_LN_IDX_WIDTH (1),

.TX_LN_DATA_WIDTH (64),

.GT_USERIO_IN_WIDTH (16),

.GT_USERIO_OUT_WIDTH (16),

.RX_BUFFER_TYPE ("NORM"),

.TX_BUFFER_TYPE ("NORM"),

.RX_BUFFER_RATIO (1)

) TI_204c_IP_inst (

//-------------------------------------------------

// Common reset and MGT related ports for the IP

//-------------------------------------------------

.master_reset_n (master_reset_n),

.mgt_freerun_clock (mgt_freerun_clock),

.mgt_refclk_p (mgt_refclk_p),

.mgt_refclk_n (mgt_refclk_n),

.mgt_gpio_in ({16{1'b0}}),

.mgt_gpio_out (mgt_gpio_out),

.qpll0_locked (qpll0_locked),

.qpll1_locked (),

.cpll_locked (),

//-------------------------------------------------

// Primary Receiver related ports (Not used here)

//-------------------------------------------------

.mgt_lane_rxp ({1'b1}),

.mgt_lane_rxn ({1'b0}),

.cfg_rx_lane_map ({1'b0}),

.cfg_rx_lane_polarity ({1'b0}),

.mgt_rx_usrclk2 (),

.rx_sys_clock (tx_sys_clock),

.rx_sync_reset (tx_sync_reset),

.cfg_rx_lane_enable ({1'b1}),

.rx_all_lanes_locked (),

.rx_release_all_lanes (1'b1),

.rx_lane_data (),

.rx_lane_data_valid (),

.rx_lane_buffer_overflow (),

.rx_lane_samples (),

.rx_lane_samples_valid (),

.rx_sync_n (),

.cfg_rx_scrambling_enabled (1'b1),

.rx_lane_configuration_data (),

.rx_lane_start_of_frame (),

.rx_lane_start_of_multiframe (),

.rx_lane_start_of_mblock (),

.rx_lane_start_of_emblock (),

.rx_lane_crc_error (),

.rx_clr_all_err_count (1'b0),

.rx_lane_invalid_somf_err_count (),

.rx_lane_clr_invalid_somf_err_count ({1'b0}),

.rx_lane_invalid_eomf_err_count (),

.rx_lane_clr_invalid_eomf_err_count ({1'b0}),

.rx_lane_invalid_eof_err_count (),

.rx_lane_clr_invalid_eof_err_count ({1'b0}),

.rx_lane_notintable_err_count (),

.rx_lane_clr_notintable_err_count ({1'b0}),

.rx_lane_disp_err_count (),

.rx_lane_clr_disp_err_count ({1'b0}),

.rx_lane_invalid_header_err_count (),

.rx_lane_clr_invalid_header_err_count ({1'b0}),

.rx_lane_invalid_eomb_err_count (),

.rx_lane_clr_invalid_eomb_err_count ({1'b0}),

.rx_lane_invalid_eoemb_err_count (),

.rx_lane_clr_invalid_eoemb_err_count ({1'b0}),

.rx_lane_crc_mismatch_err_count (),

.rx_lane_clr_crc_mismatch_err_count ({1'b0}),

.rx_sysref (1'b0),

.rx_lmfc_pulse (),

.rx_lemc_pulse (),

.rx_sysref_realign_count (),

.rx_clr_sysref_realign_count (1'b0),

.cfg_rx_det_latency_en (1'b1),

.cfg_rx_buffer_release_delay ({10{1'b0}}),

.rx_lmfc_to_buffer_release_delay (),

.rx_lemc_to_buffer_release_delay (),

//-------------------------------------------------

// Primary Transmitter related ports

//-------------------------------------------------

.mgt_lane_txp (mgt_lane_txp),

.mgt_lane_txn (mgt_lane_txn),

.cfg_tx_lane_map ({1'b0}),

.cfg_tx_lane_polarity ({1'b0}),

.mgt_tx_usrclk2 (mgt_tx_usrclk2),

.tx_sys_clock (tx_sys_clock),

.tx_sync_reset (tx_sync_reset),

.cfg_tx_lane_enable ({1'b1}),

.tx_lane_data (internal_tx_lane_data),

.tx_lane_data_ready (tx_lane_data_ready),

.tx_sync_n (1'b0),

.cfg_tx_scrambling_enabled (1'b1),

.cfg_tx_ilas_test_mode (1'b0),

.tx_lane_start_of_frame (),

.tx_lane_start_of_multiframe (),

.tx_lane_start_of_mblock (tx_lane_start_of_mblock),

.tx_lane_start_of_emblock (tx_lane_start_of_emblock),

.tx_sysref (tx_sysref),

.tx_lmfc_pulse (),

.tx_lemc_pulse (tx_lemc_pulse_int),

.tx_sysref_realign_count (tx_sysref_realign_count),

.tx_clr_sysref_realign_count (tx_clr_sysref_realign_count),

.testport1_in ({16{1'b0}}),

.testport1_out (),

.testport2_in ({16{1'b0}}),

.testport2_out (),

.testport3_in ({16{1'b0}}),

.testport3_out ()

);

我在做什么错?

谢谢你