Other Parts Discussed in Thread: DAC38J84, LMK04828

主题中讨论的其他器件:DAC38J84、 LMK04828

工具与软件:

您好!

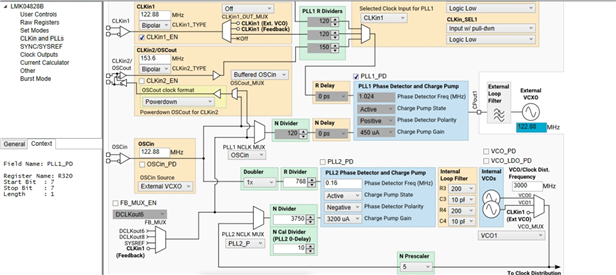

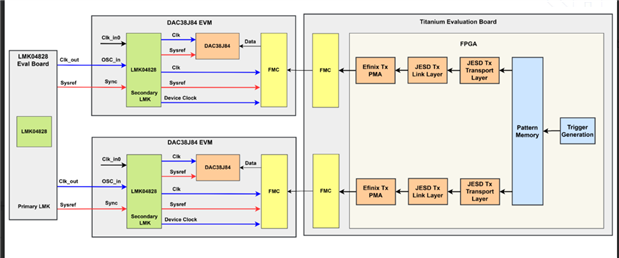

我们正在尝试使用零延迟模式来实现多 DAC 同步(使用2个 DAC38J84 EVM 和 Efinix Ti3775N1156 FPGA)、从而生成以下时钟。

器件时钟= 125 MHz

DAC_Clk = 1000 MHz

PMA 时钟= 100 MHz

Sysref = 3.90625 MHz。 (数据速率 = 5Gbps、内插值= x4)。

主 LMK04828将为 DAC EVM 上的辅助 LMK04828提供参考时钟、如下所示。

我的问题是:

1) 1)我们的时钟配置是否朝正确的方向发展。 我们是否可以采用此设置进行多芯片 DAC 同步?

2)有两种 ZDM 变体、即正常 ZDM 和嵌套 ZDM。 哪一个更适合我们的情况?

如果需要更多信息、请告知我们。 提出改进建议将非常有用。