器件型号:ADC3664EVM

工具与软件:

尊敬的技术支持团队:

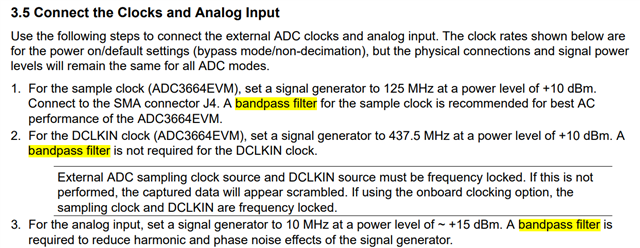

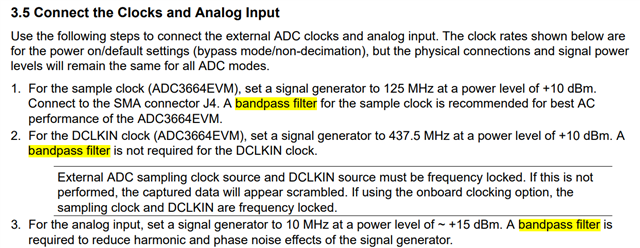

对于用户指南、DCLK 和采样时钟输入电平应+10dBm。

以下哪一项设置来自外部脉冲发生器的正弦波(10dBm=2Vpp)或方波(Vpp=1.414Vpp)是正确的?

我的函数发生器无法设置437.5MHz 方波。

用户指南介绍了需要采样时钟和模拟输入来获得良好的性能。

它是否意味着信号发生器设置? 或者在电路板电路上实现它?

如果您有任何示例、可以与我们分享吗?

此致、

TTD

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号:ADC3664EVM

工具与软件:

尊敬的技术支持团队:

对于用户指南、DCLK 和采样时钟输入电平应+10dBm。

以下哪一项设置来自外部脉冲发生器的正弦波(10dBm=2Vpp)或方波(Vpp=1.414Vpp)是正确的?

我的函数发生器无法设置437.5MHz 方波。

用户指南介绍了需要采样时钟和模拟输入来获得良好的性能。

它是否意味着信号发生器设置? 或者在电路板电路上实现它?

如果您有任何示例、可以与我们分享吗?

此致、

TTD

您好、TTD:

用户指南中有错误。 请使用正弦波并将电平设置为0到+2dBm (最大值)

对于 DCLKIN、如果函数发生器足够干净、您可以使用函数发生器。 不过、最好使用高质量低抖动(纯净)信号发生器。

一些示例包括 R&S 的 SMA100A 或 SMA100B、或者 Agilent 8257D。 以上任一选项都需要安装低抖动选项。

每个信号发生器都需要在 sig 发生器的输出和 EVM 上的输入 SMA 连接器之间串联一个带通滤波器。

这是一个通用 pic。

此致、

Rob

尊敬的 Rob:

感谢您的答复。

我得到了您所示 BPF 的插入位置。

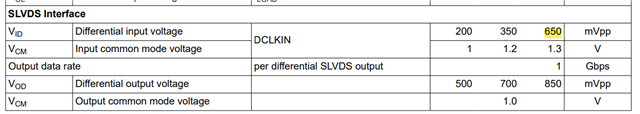

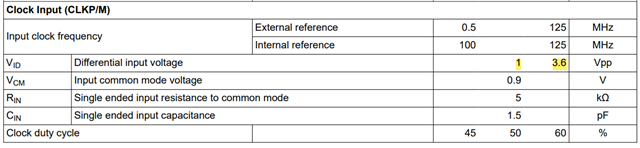

DCLIN (650mVpp 最大值)的最大值是否为2dBm (0.796Vpp 正弦波)?

采样时钟的 CLKP/M 的 VID 为1Vpp (typ)和3.6V3874 ((max))。

看来 2dBm (0.796Vpp) 不够级别。

如果我的理解不正确、您能建议吗?

我还有一个有关 ADC3644EVM (CMOS 接口)的问题。

我的配置是旁路模式、那么 ADC3644EVM 不需要外部时钟来对时钟和 DCLKIN 进行采样?

尊敬的 Rob:

很抱歉、ADC3664和 ADC3644之间的器件型号稍有不同。

我已经拥有 ADC3664EVM (SLVDS)和 ADC3644EVM (DDR CMOS)。现已从 TI 发货(我尚未拥有)。

ADC3644EVM (使用 DDR CMOS、14位、旁路)支持基于数据表的125MHz 采样时钟板载时钟(CECE6214)。

据我了解、 ADC3664EVM (SLVDS) 不支持 CDC (需要外部时钟)。

此致、

TTD