主题中讨论的其他器件: DLPC910

大家好、

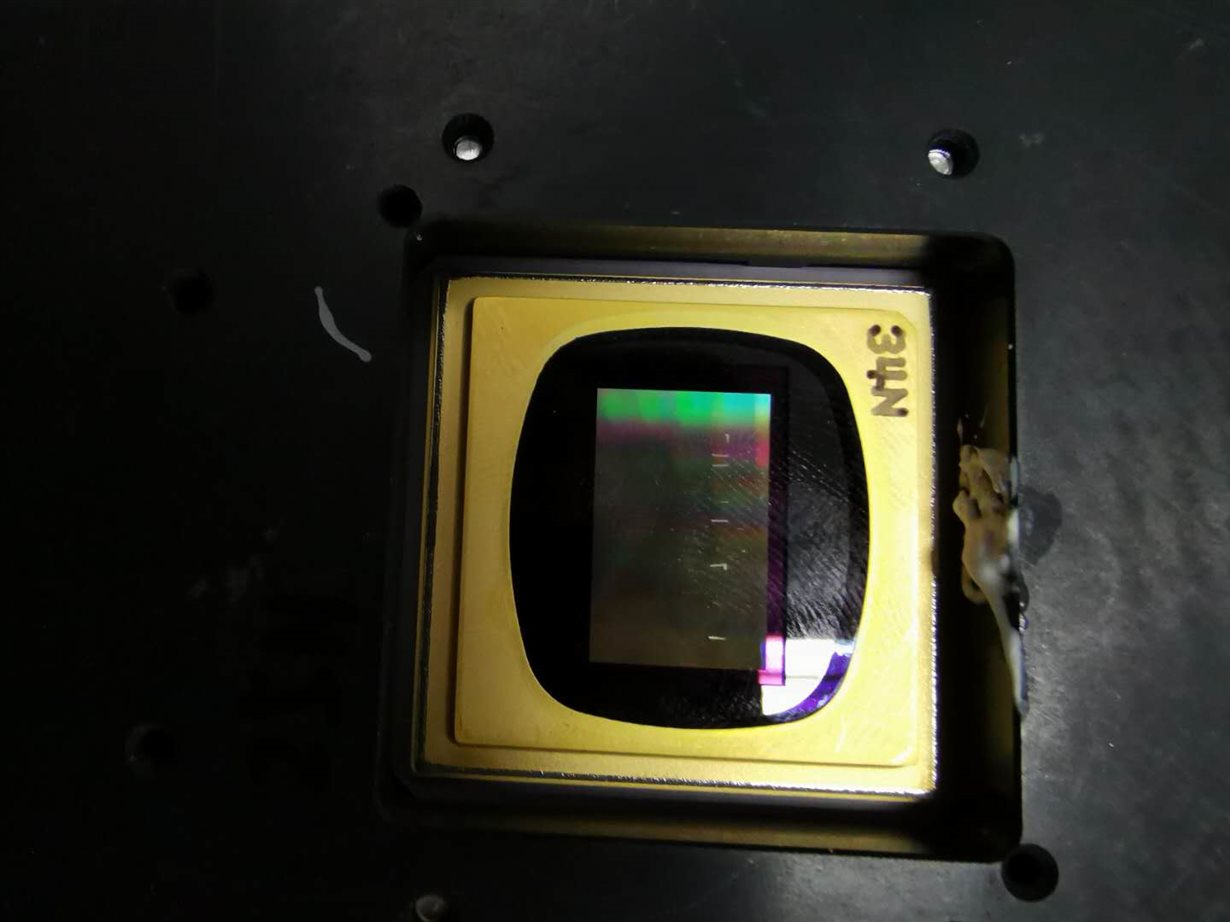

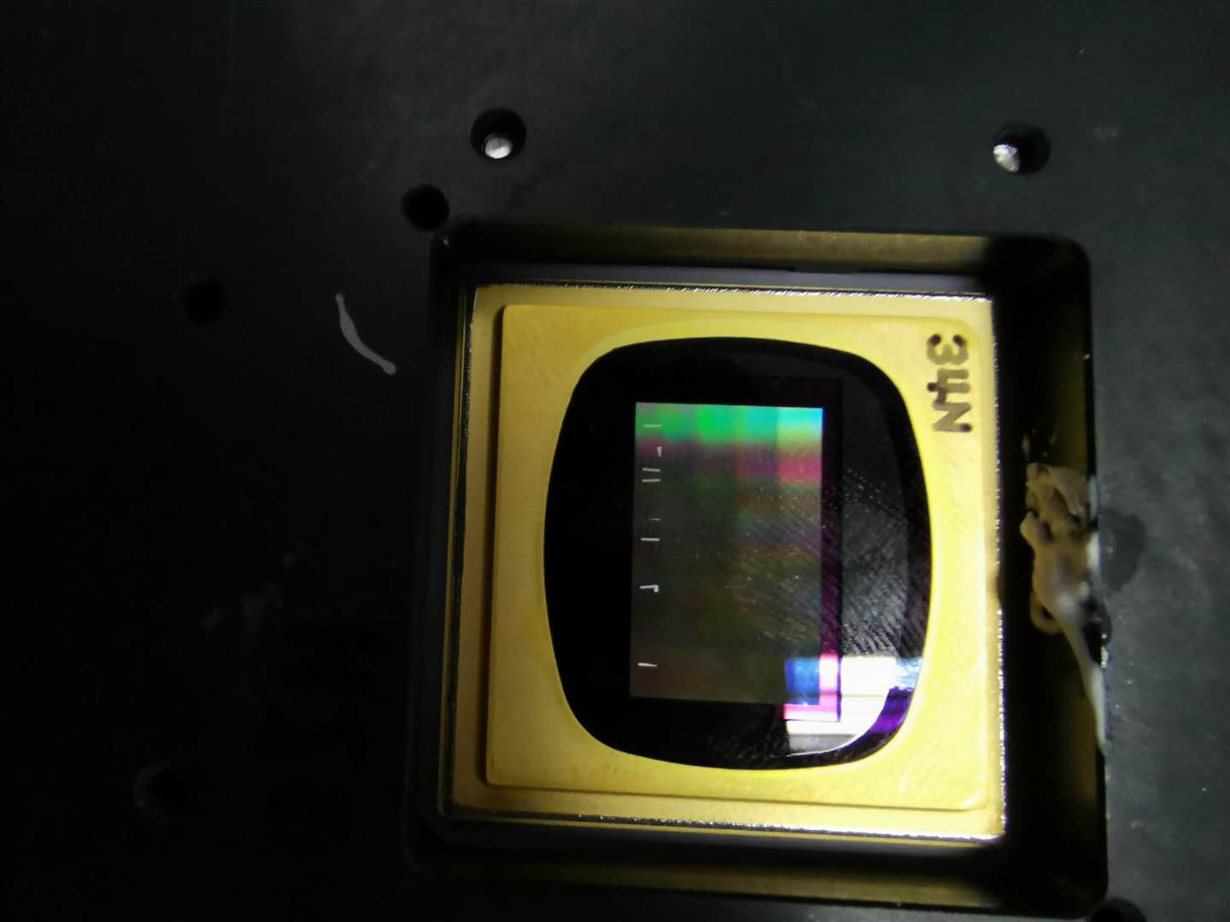

我们一直在驱动 DLP9000X DMD、但失败了。 当我将数据模式加载到 DMD 中时、DMD。上不存在任何内容

1.ecP2_finished status is correct (High) when I power on our PCB driver board (当我打开 PCB 驱动板时,ECP2_finished 状态为正确(高))。

2.VLED0和 VLED1状态正确。

我可以通过应用 FPGA 调试工具(Xilinx ISE Chipscope)获取 DMD_TYPE (3:0)="1111"和 DDC_VERSION (2:0)="010"

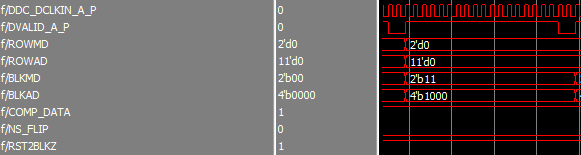

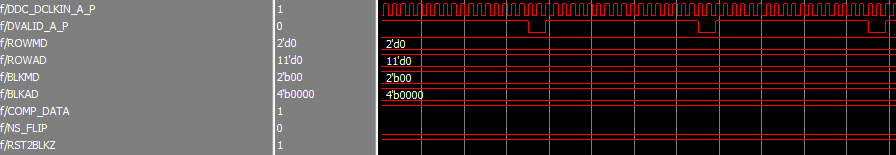

4.将应用测试文件下载到应用程序 FPGA 后,我发现 RST_ACTIVE 的状态不正确(HIGH -> LOW,,但我没有将任何内容加载到 DMD 中)。

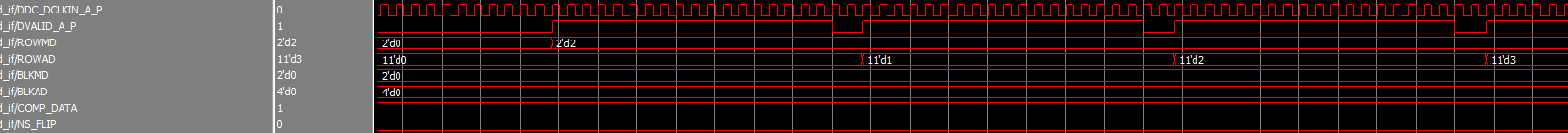

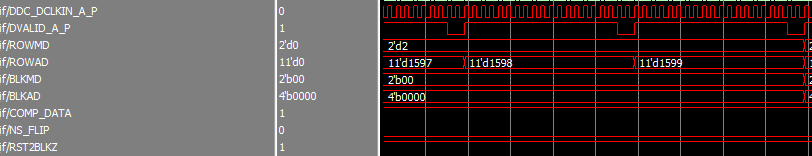

5.我将数据加载到 DMD 中(加载1600行,然后全局复位),但 DMD 上没有任何数据。

接下来该怎么做、如何进行调试?

谢谢!