主题中讨论的其他器件:DLPC4422、

您好、TI 团队!

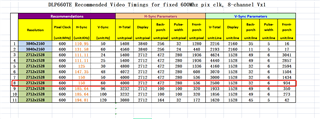

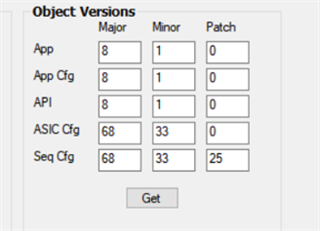

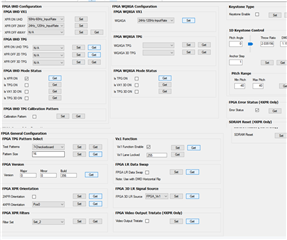

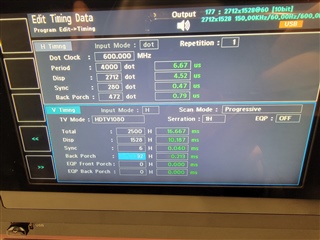

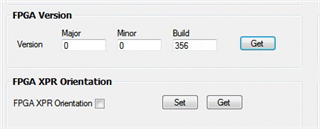

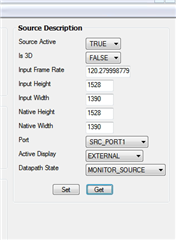

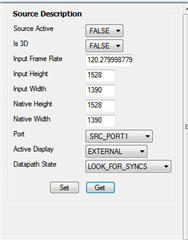

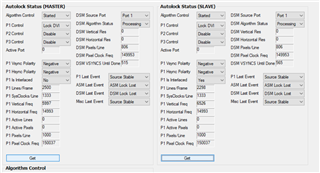

虽然我之前曾问过如何显示 DMD 原生像素、但我们的供应商迄今已尝试修改几乎所有的 timimg 参数、但对于2712x1528输入信号仍然无法正确显示、即只要把 XPR 设置为2WAY 模式、就没有图像了。

希望 TI 的工程师能继续帮我们解决这个问题。

您能提供一些有关调试 vby1的建议吗?

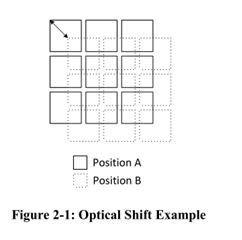

我的要求是使用原生像素、以便 DMD 图片不会抖动。 因为我测试过、如果投影仪在 UHD 模式下处于 XPR 或在 UHD TPG 模式下处于 XPR、DMD 的像素将向上、向下、向左和向右抖动。 如果投影仪处于 XPR OFF UHD TPG 模式、则 DMD 的像素将不会抖动。 因此我想使用 XPR 关闭2WAY 模式。

我还尝试了删除工程文件中 XRP 的所有配置和参数、然后更新 ASIC 闪存、但只要它处于 XPR 开启模式、DMD 的像素就仍然会抖动。

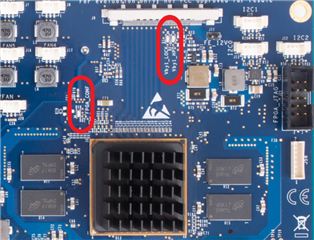

此外、我想知道您之前测试的前端电路板中使用了什么芯片。 此前端电路板能否提供购买链接或代理?