您好!

我目前正在设计 DLPC910平台、有两个问题。

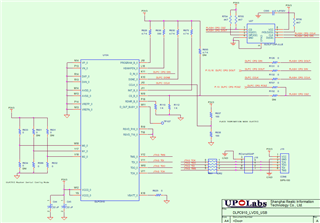

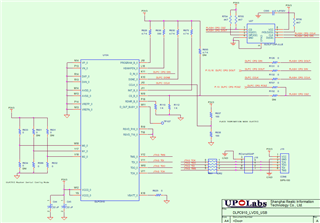

1. 由于 DLPR 芯片停产、DLPC910目前使用 SPI 闪存作为配置器件。 我设计的原理图如下所示。 如果有任何问题、请帮我检查。

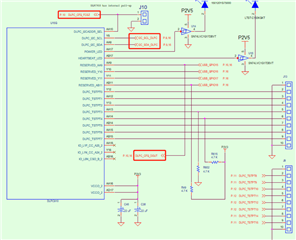

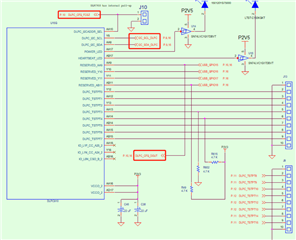

2. 在 DLPC910EVM 中存在很多 TSTP 信号、但在实际应用中不需要这些信号。 在下图中、除了标记为红色的信号外、是否可以省略所有信号、即引脚是悬空的。

谢谢!

晴天

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我目前正在设计 DLPC910平台、有两个问题。

1. 由于 DLPR 芯片停产、DLPC910目前使用 SPI 闪存作为配置器件。 我设计的原理图如下所示。 如果有任何问题、请帮我检查。

2. 在 DLPC910EVM 中存在很多 TSTP 信号、但在实际应用中不需要这些信号。 在下图中、除了标记为红色的信号外、是否可以省略所有信号、即引脚是悬空的。

谢谢!

晴天

您好、Sunny、

1.我看了一下您上面发布的第一个原理图、而且想知道您的 JTAG 接头的器件型号。 我试图根据我认为是"SIP6-100"来查找它、但我无法找到此部件。 这是自定义吗?

我们拥有的原始收割台旨在与 Digvoice JTAG-HS2编程器配合使用、该编程器用于高速数据。

请允许我有更多时间扩展您在连接器之间添加的电阻网络和外部保护。

2. 根据用户指南,DLPC_TSTPT 8到15被保留给 TI 内部使用。 删除此部分不存在任何问题、但请允许我在同事明天下午回来时向他咨询、以防这些最终对您有用。 我还会问他更多有关 USB GPIO 的信息、但您的图像上圈出的信号看起来是正确的。 您当然需要这些驱动器。

此致、

迈克尔·莱

您好、Sunny、

我刚刚完成了与同事讨论这个问题的过程。 我们都认为您可以移除测试点 DLPC_TSTPT 0到15、因为它们都是 TI 内部测试点。 但是、如果您想将这些接地点替换为可探测的硬件接地环路、在电路板周围设置额外的接地点确实很有用。 过去、这在调试时已证明非常有用。

另请确保您仅使 USB_GPIO15悬空并保持与 DLPC_CONFIG_DOUT 网络的连接。

请确保您使用的 SPI PROM 与 DLPC910电路板上的 Xilinx Virtex V FPGA 兼容、如果您拥有的芯片不兼容、请查找兼容芯片。

此致、

迈克尔·莱