主题中讨论的其他器件: DLP4620SQ1EVM、 DLP4621-Q1、DLPC231-Q1

工具与软件:

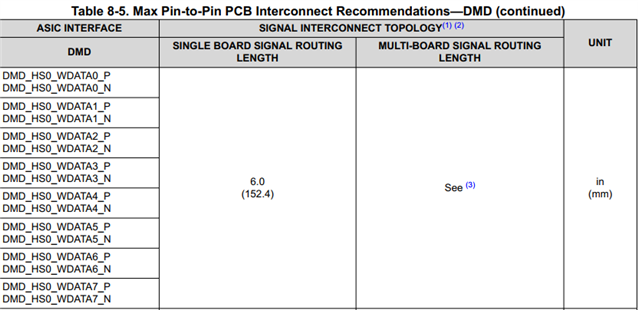

在 DLPC231S-Q1数据表中、高速数据线存在限制。

单板情况下的最大图形长度为152.4mm。

目前、在我们的设计中、这些信号图形长度大约大10~20mm。

我的问题是、如果由于图形长度导致显示不正常、我可以做什么。

如果将 PATTEN 内长度(例如时钟线和数据线)调整为几乎相同的长度、则可以增加最大图形长度?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

在 DLPC231S-Q1数据表中、高速数据线存在限制。

单板情况下的最大图形长度为152.4mm。

目前、在我们的设计中、这些信号图形长度大约大10~20mm。

我的问题是、如果由于图形长度导致显示不正常、我可以做什么。

如果将 PATTEN 内长度(例如时钟线和数据线)调整为几乎相同的长度、则可以增加最大图形长度?

Jin、

该设计是否已通过物理实现? 您是否了解过我们如何布局 DLP4620SQ1EVM 的 TI 参考设计? 这应该会为您提供良好的参考。

如果您有一个多板设计、我建议您尽量进行仿真。 我们已经看到、即使我们的2xLVDS 控制器使用长度超过6英寸的柔性电缆、因此鉴于 DLPC231使用 subLVDS、您可能可以额外增加20mm。

下面是一个设计检查清单常见问题解答、可帮助您解决问题。 如果有任何其他问题、请联系我们、我很乐意提供帮助!

此致、

Michael Ly

我们的设计几乎是固定的、目前 subLVDS 线路的最大长度约为155mm。

我认为将 subLVDS 线图形长度限制在最大6英寸的原因有很多。

但是、您说图形长度在20毫米(即6英寸)以内将很好。 这对我来说是个好消息。

我又收到一个问题。 正如我听说的 TI FAE 一样、开放式 LDI 接口(LVDS)限制了线对间的长度。

建议对间的最大差值为5mil。 大约为0.127毫米。

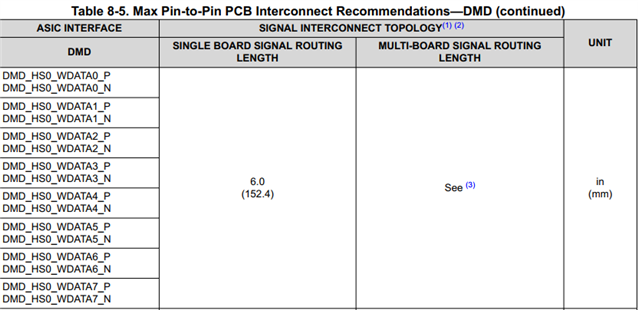

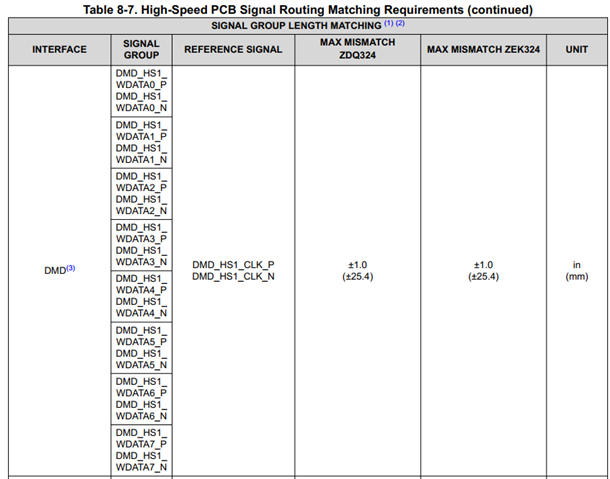

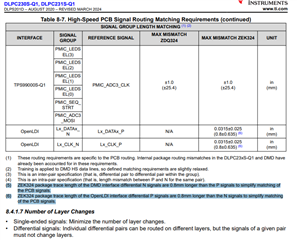

但根据产品说明书、clk 对和其他数据对长度差限制为25.4mm。

与 LDI 开路(也称为 LVDS)相比、这是一个非常大的差距。

如果 clk 和数据之间的长度差约为20mm、那真的没有问题吗?

尊敬的 Jin:

请耐心听我的解释,你已派我的表。

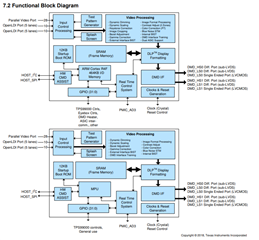

您在该表中展示的基准是 DLPC231-Q1 DMD 控制器和 DLP4621-Q1 DMD 之间的连接。

OLDI 接口位于 OLDI 的控制器和连接器之间:

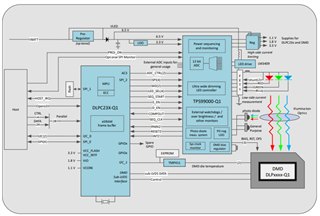

在第一张图片中、我们看到 OLDI 向控制器发送数据包、控制器随后通过各个控制 块处理数据。 然后、处理后的数据将格式化为 DMD 能够理解的格式、并通过 DMD_HS*和 DMD_LS*端口。 这是您在展示的表中引用的内容。

要回答您的问题、请参阅以下内容、了解 DLPC23x 数据表中的指南:

上面的数据表明最大失配度为 0.0315±0.025英寸(或0.8±0.635毫米)。

这可以回答您的问题吗?

此致、

Michael Ly

Jin、

我不确定是否已经向您发送了这份电子邮件、但我们还有一份原理图和布局设计检查清单。 如果您尚未了解这一点、我强烈建议您使用它、以确保您的设计首次生效、或帮助您获得初始的概念验证。

我最近推出了这项功能、并尝试鼓励更多客户提问。 感谢您联系我们、如果您希望获得额外支持、请继续这样做。

此致、

Michael Ly

这不是我的问题的答案。

我的问题是 clk 和数据之间的长度匹配。

在 DLPC231S-Q1数据表中、DMD HS clk 和 DMD HS 数据之间的长度差限制低于25.4mm。

与 Open LDI 要求相比、该数字非常大、即 clk 和数据长度差异小于0.127mm。

开放式 LDI 是 LVDS 接口、而 DMD HS 接口是 sub-LVDS。

我想两者都是相似的。 但为什么要求差异很大?

如果 DMD HS 导致时钟和数据之间的延迟差超过20mm、您是否有任何仿真或测试结果?

Jin、

要求差异之所以大的原因是 DMD HS 接口经过高速(HS)培训。 此训练会扫描一系列值、并确定哪个值最好。 此测试持续运行以确保控制器- DMD 接口工作正常。 这显示在上面显示的表8-7的注释2中。

OLDI 不会进行 HS 训练、因此容差要小得多。

此致、

Michael Ly

P.S.回到您原始的关于额外长度20mm 的问题:请确保您仍在针对您的设计进行尽可能多的仿真、尤其是在多板的情况下。