工具与软件:

PHY DP83825I 的上电序列出现了问题。 电气特性表"图5-1 "中所示。 上电时序"中 增加了以下信息:"时钟应在功率斜坡时可用。 否则、请将 RESET_N 保持在低电平并在时钟稳定后至少100us 释放它。"

通过调查、我们假设我们实施 PHY 违反了此义务:

首先、我们测量了 XI 是否在 VAVDD 的功率斜坡上可用:

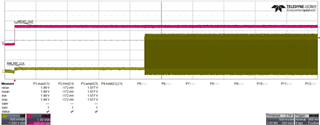

该图片显示了 SOM 的复位序列。 VDD3V3A 与 VAVDD 相连、RMII_REF_CLK 与 XI 相连。可以看到、该时钟在电源斜坡上不可用。

其次、我们测量了时钟相对于全局复位信号何时是稳定的:

可以看到、连接到 RESET_N 的 X_nRESET_OUT 在时钟稳定后的至少100us 内未保持低电平。 RESET_N 由 SOM 上的 PMIC 控制、因此信号不能一直保持到时钟启动、因为时钟由处理器和处理器提供(如果受到 RESET 信号的影响)。

那么问题是、我们的实现可能会导致哪些问题、以及是否需要通过 MDIO 接口进行额外的软件复位。