请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TCAN4550-Q1 主题中讨论的其他器件: TCAN4550

工具与软件:

尊敬的团队

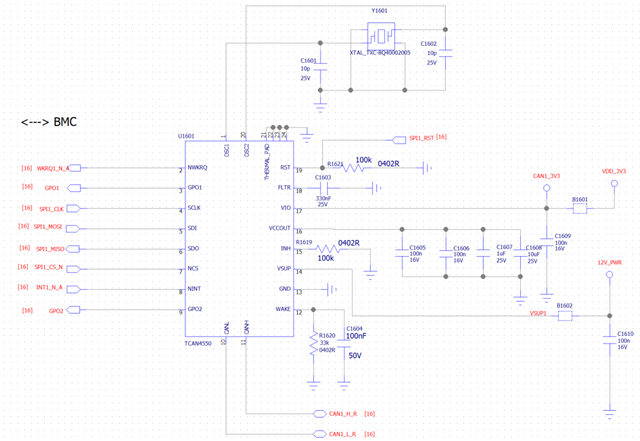

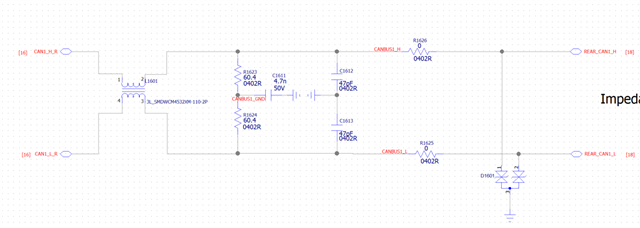

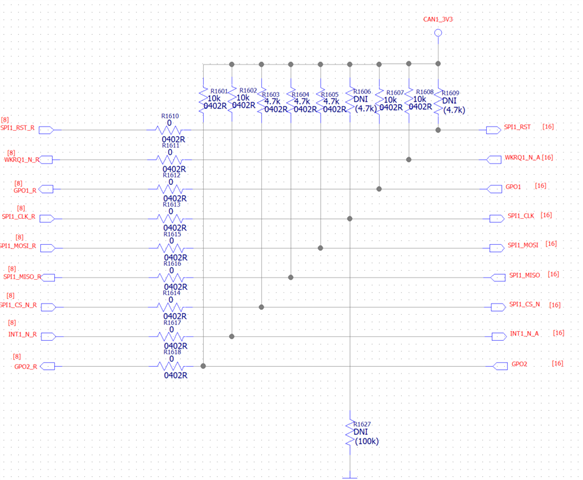

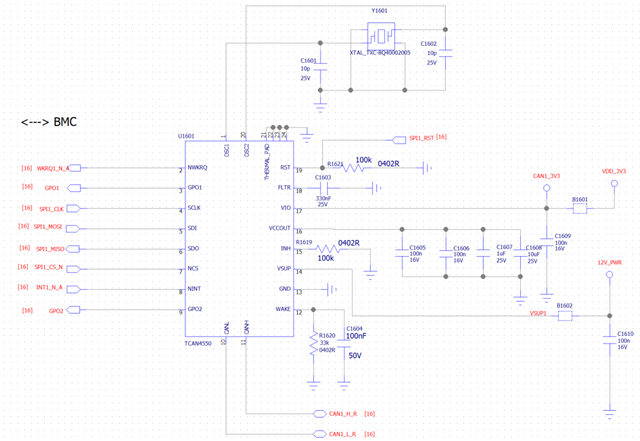

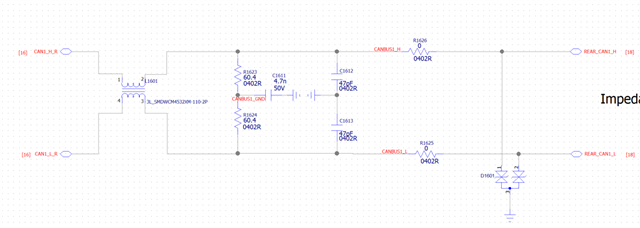

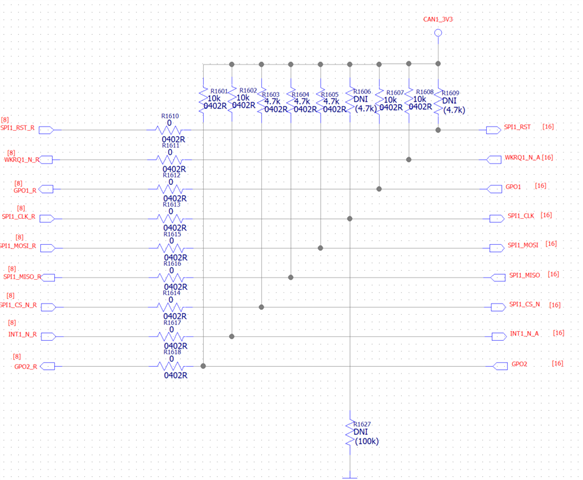

我们 在客户的新项目中采用 TCAN4550-Q1进行设计。

您能帮助复查原理图吗?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的团队

我们 在客户的新项目中采用 TCAN4550-Q1进行设计。

您能帮助复查原理图吗?

谢谢

Jeremy、您好!

我已经查看了原理图并评论了以下内容:

此致、

Jonathan

Jeremy、您好!

GPO2是否需要上拉3.3V?

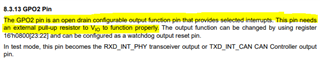

有。 请参阅数据表中的说明。

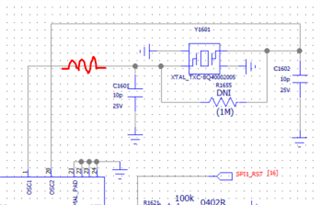

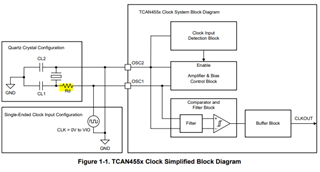

对于 OSC1引脚和晶体之间串联电阻的建议、我没有讨论 OSC1和 OSC2引脚之间的1M 电阻器。 TCAN4550-Q1在 OSC1和 OSC2之间已有一个内部500k 电阻器。 而是讨论直接位于 OSC1引脚与负载电容器和晶体之间的串联电阻器。 该电阻的作用是帮助减少流经晶体的电流量、并在必要时降低驱动电平或功率损耗。

此致、

Jonathan