工具/软件:

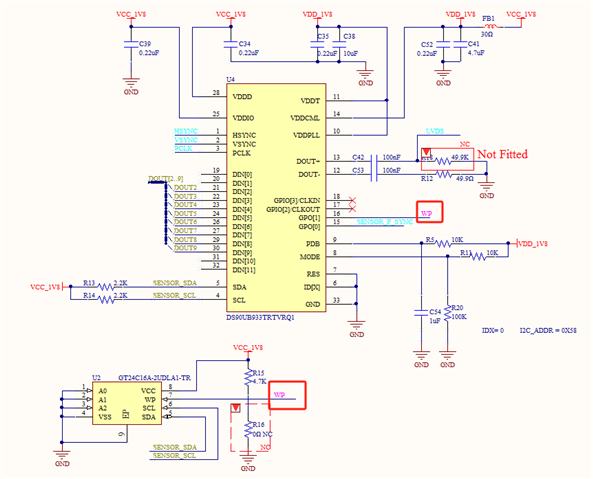

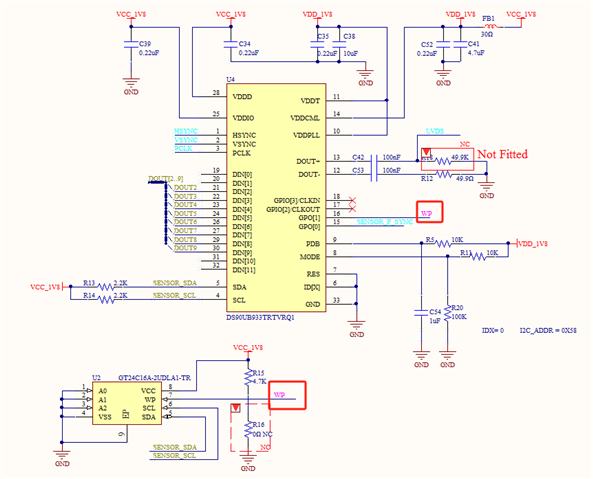

1.当前外围电路是否有问题

上电后、我们需要 WP 引脚保持高电平。 我们可以配置0x0D 寄存器来实现这一点吗? 目前、在测试期间、我们发现初始上电将为高电平、但它将被下拉、然后再次上拉

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

1.当前外围电路是否有问题

上电后、我们需要 WP 引脚保持高电平。 我们可以配置0x0D 寄存器来实现这一点吗? 目前、在测试期间、我们发现初始上电将为高电平、但它将被下拉、然后再次上拉

我们要实现的当前功能是从外部将 WP 连接到该串行器/解串器的引脚。 我们只需要在 Eepro 燃烧过程中将其拉低,并在任何其他时间保持高电平。 我们要确认的当前问题是:1. 能否实现连接到 GPO1端口的当前情况、即芯片上电时引脚被拉高? 如果可能、请提供寄存器的配置。

2.如果 GPO1不工作、是否有推荐的接口来实现此功能并提供寄存器的配置。

此外、我们需要确认我们测量的 GPO1波形。 此寄存器的0x0D 配置为(0x05)高阻抗状态、但这有点奇怪。 外部电路有一个上拉电阻器、那么为什么仍然存在高电平和低电平、还有两次呢? 请同时确认这一点。