Other Parts Discussed in Thread: SN75LVDS84A, SN75LVDS82, FLINK3V8BT-85

Thread 中讨论的其他器件: SN75LVDS82、 FLINK3V8BT-85

工具/软件:

您好、TI 人

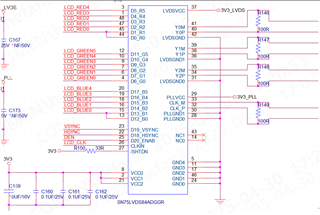

我的客户使用 SN75LVDS84A 和 THC63LVDF84C 作为 RGB 转 LVDS 和 LVDS 转 RGB 桥接至屏幕。

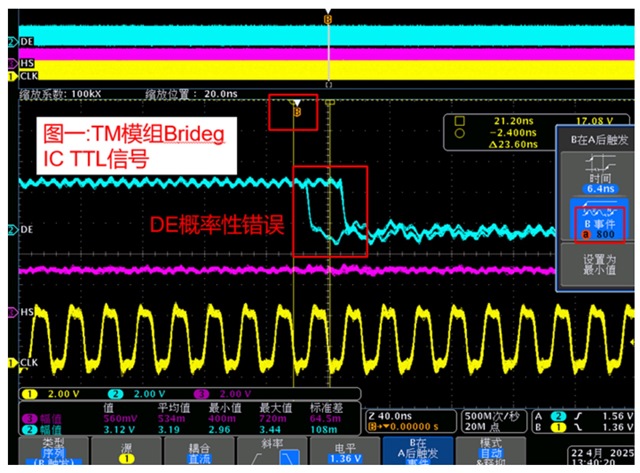

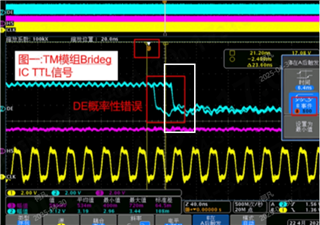

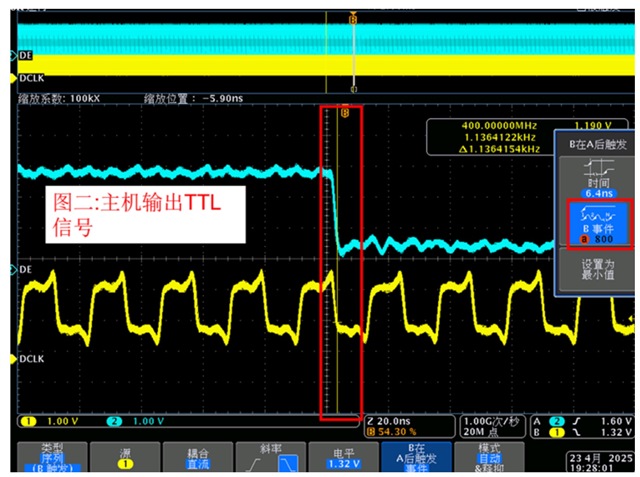

我们遇到一个问题是信号抖动,一些时间信号包含多个时钟。 有时不会。

它们会探测 THC63LVDF84C DE 输出。 但他们会进行 ABA 测试、我们发现问题出在 SN75LVDS84A。

那么、您是否可以通过某种方法来检查 LVDS 输出是否正确?

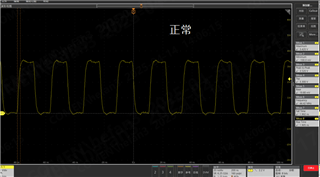

我们还探测 SN75LVDS84A 中的 DE 信号输入、该输入没有抖动、

SN75LVDS84A 输入时的 DE。

THC63LVDF84C 输出端的 DE: