工具/软件:

尊敬的 TI 支持部门:

我目前正在使用进行设计 TUSB8041RGC 在分析的原理图时所需执行的操作 TUSB8041RGC EVM (修订版 D) 、我注意到晶体负载电容器不匹配。

在 EVM 设计中、 C1和 C2均为18 pF 。

不过、 此设计中使用的晶体的负载电容(CL)为20 pF 选择 ESD 二极管。

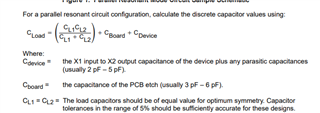

当我应用标准公式时:

C1=C2=2×(CL−寄生电容) C1 = C2 = 2次(CL - C_{parasitic })C1=C2=2×(CL−寄生电容)

得到的结果是 32 pF 假设典型寄生电容为4 pF。 这与 EVM 使用的18个 pF 大不相同。

您能帮助澄清一下:

-

假设该布局中的寄生电容高得多?

-

18 pF 是错误的还是有意的?

-

我是否应该在设计中使用像32 pF 这样的器件?

提前感谢您的澄清。