工具/软件:

尊敬的团队:

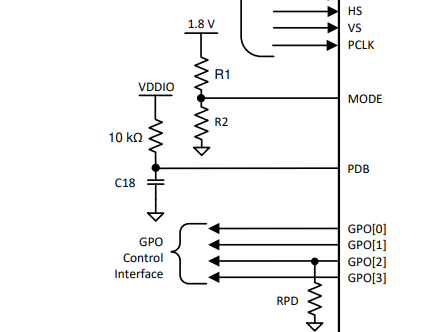

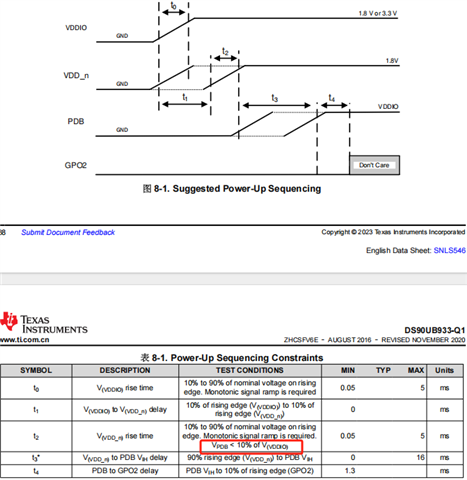

为了满足 PDB 引脚外部电路的 T3上升时间要求、根据数据表中的上拉电阻10k、下拉电 容1uF、需要、Ω。

现在 、我们将下拉 电容更改为0.1uF、 上拉电阻10K 不变。开通时间缩短、μ s。

将上电完成时间提前到、然后再读取 EEPROM。

您能否帮助确认变更计划(10K 和0.1uF)是否正常?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的团队:

为了满足 PDB 引脚外部电路的 T3上升时间要求、根据数据表中的上拉电阻10k、下拉电 容1uF、需要、Ω。

现在 、我们将下拉 电容更改为0.1uF、 上拉电阻10K 不变。开通时间缩短、μ s。

将上电完成时间提前到、然后再读取 EEPROM。

您能否帮助确认变更计划(10K 和0.1uF)是否正常?

您好 Zoe、

谢谢。

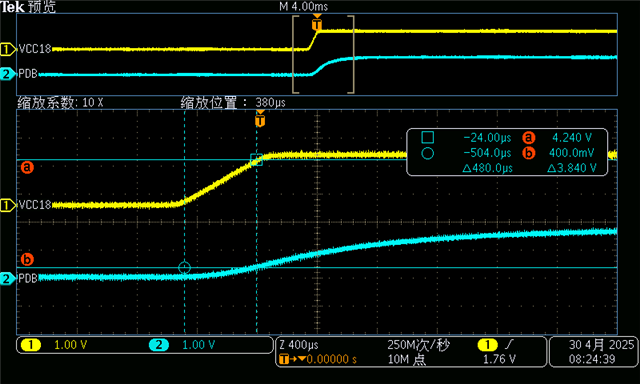

修改 PDB 外设 RC 电路(10K 和0.1uF)后。 在测试和验证过程中、发现附件中"规格"红色框内的 VPDB 不满足低于 VDDIO (0.18V) 10%的要求。

测试修改后的电路后、当 T2达到90%时、V-PDB 的电压为0.4V、这不符合 V-PDB<VDDIO (0.18V)的10%的要求、但不超过 V-PDB IL 设置的 V-PDB (0.35 * 1.8V=0.63V)、并且仍处于低电平状态。

您能否帮助确认 PDB 点的当前外围电路状态(10K 和0.1uF)是否会影响其功能? 您是否需要进行任何更改? 如果需要更改、请提供建议。