请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83825I 工具/软件:

我想问一个有关上电顺序的问题。

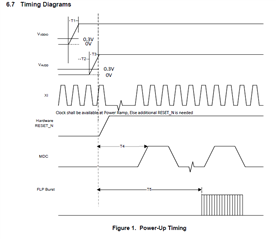

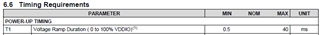

根据数据表、T1需要超过0.5ms、但注意(1)说"如果在功率斜升后提供时钟、则需要在时钟可用后对 PHY 进行外部复位"。

说 VDDIO 斜升后复位应有效一段时间的说法是否正确?

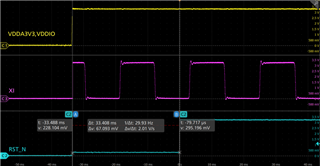

在我们的原型板中、上电序列如图所示、复位在接通电源后33ms 释放。

我想就这种行为是否有问题提供建议。

此致。