主题中讨论的其他器件: ESD2CAN24-Q1

工具/软件:

尊敬的 TI 专家:

我的客户使用 TCAN1044-Q1制作了原理图。 您能查看此原理图并检查一些问题吗?

1.请检查是否有任何问题需要修复,以获得更好的性能。

2.您能否检查操作 STB 引脚所需的最小上拉电流值? 因为我们需要检查它是否低于 MCU 可以发送的值。

在数据表中从哪里可以找到基础?

3.是否应该为 TXD 和 RXD 引脚添加上拉或下拉电阻器?

请检查此问题。 谢谢。

此致、

追逐

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的 TI 专家:

我的客户使用 TCAN1044-Q1制作了原理图。 您能查看此原理图并检查一些问题吗?

1.请检查是否有任何问题需要修复,以获得更好的性能。

2.您能否检查操作 STB 引脚所需的最小上拉电流值? 因为我们需要检查它是否低于 MCU 可以发送的值。

在数据表中从哪里可以找到基础?

3.是否应该为 TXD 和 RXD 引脚添加上拉或下拉电阻器?

请检查此问题。 谢谢。

此致、

追逐

您好 Chase、

1. 0欧姆占位件(需要时可重新调整)可放置在 RXD/TXD 上、分裂终端应为每个60k Ω 和4.7nF (除非所选元件是根据系统需求而设计)、ESD 可放置在更靠近总线电容后连接器的位置。 请面向 CAN 应用推广 ESD2CAN24-Q1。

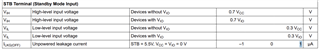

2. 请参阅以下内容:

3.不需要,仅当控制器的 TXD 输出为开漏时,谢谢。

此致、

Michael。

您好 Chase、

CAN 物理层要求系统中的两个节点具有120 Ω 端接、CANH 和 CANL 之间总共为60 Ω。 未端接节点可能包括部分端接、以帮助抑制信号反射、只要总线总负载不会受到太大的影响-这将取决于包含部分端接的节点数量、因为每个节点都会向总线添加额外的负载。 对于相对较小的系统(十几个节点)、22k 欧姆的部分端接没问题、因为这将使等效负载保持在58欧姆左右(TCAN1145规定在扩展负载条件下、性能可低至50欧姆或45欧姆)。

分裂终端的电容范围通常为4.7nF - 100nF、常见值为4.7nF。 除非特别关注目标噪声频率、否则此处47nF 没有出现任何问题(这种情况并不常见)。

STB 引脚具有一个连接到 Vio (或 Vcc)的内部上拉电阻。 为了驱动低电平输入、MCU 需要从该上拉电阻吸收电流、并且能够驱动该引脚上的低电平电压。 此引脚的 IIL 规范描述了一个测试用例、其中当 Vio 上拉基准为5.5V 时、向 STB 施加0V。 内部上拉产生的输出电流最大值为20uA、这意味着信号驱动器(应用案例中的 MCU)需要驱动20uA 或更低的电流才能在此引脚上驱动低电平电压。 由于这是一种非常弱的内部偏置、因此几乎任何 MCU 都能够驱动它而不会出现问题。

如果您有任何其他问题、请告诉我。

此致、

Eric Schott

您好 Chase、

CAN 物理层要求系统中的两个节点具有120 Ω 端接、CANH 和 CANL 之间总共为60 Ω。 未端接节点可能包括部分端接、以帮助抑制信号反射、只要总线总负载不会受到太大的影响-这将取决于包含部分端接的节点数量、因为每个节点都会向总线添加额外的负载。 对于相对较小的系统(十几个节点)、22k 欧姆的部分端接没问题、因为这将使等效负载保持在58欧姆左右(TCAN1145规定在扩展负载条件下、性能可低至50欧姆或45欧姆)。

分裂终端的电容范围通常为4.7nF - 100nF、常见值为4.7nF。 除非特别关注目标噪声频率、否则此处47nF 没有出现任何问题(这种情况并不常见)。

STB 引脚具有一个连接到 Vio (或 Vcc)的内部上拉电阻。 为了驱动低电平输入、MCU 需要从该上拉电阻吸收电流、并且能够驱动该引脚上的低电平电压。 此引脚的 IIL 规范描述了一个测试用例、其中当 Vio 上拉基准为5.5V 时、向 STB 施加0V。 内部上拉产生的输出电流最大值为20uA、这意味着信号驱动器(应用案例中的 MCU)需要驱动20uA 或更低的电流才能在此引脚上驱动低电平电压。 由于这是一种非常弱的内部偏置、因此几乎任何 MCU 都能够驱动它而不会出现问题。

如果您有任何其他问题、请告诉我。

此致、

Eric Schott